Other Parts Discussed in Thread: ADS112C04

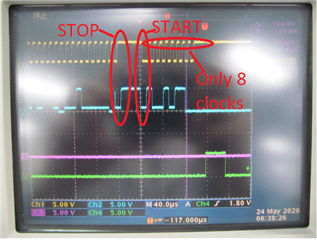

When a write or read process is performed in I2C communication, the slave side fixes the SDA to Low. As a countermeasure, a command to read the conversion completion in ADS 1119 was added before reading the AD conversion, but an error recurred. Please tell me if there are any measures. I will answer any questions about the environment and software. Also, if this error continues, I am thinking of changing to ADS 112 c04, but will the same error occur?