Hi,

I'm currently working on ADS125H02 interfacing with MSP432P4111. In this I'm using single ended operation.

AIN0 - AINCOM and GAIN is 0.5 - which is 0v to +- 5v

my analog input to AIN0 is 1v and -0.5.

as far as now I'm getting the SPI response perfectly, but my issue is in RDATA

where I'm reading my output for this I have some questions

In program - It is mandatory to give OFCAL and FULCAL register before RDATA and after START command.

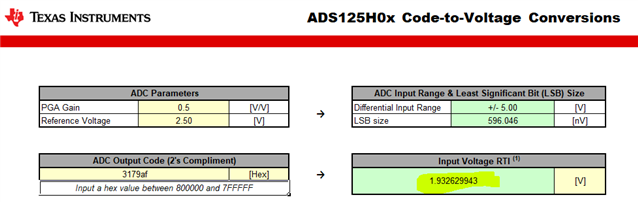

In calculation - once I get my 24bit conversion for example:

AIN0 - 0.3 V

MSB - 31

MID - 79

LSB - AF

Then I converted this hex value into decimal and applied in formula - CONVERSION DATA * VREF / (2^24).

Is this formula correct or not if it isn't then which formula to use.

does my procedure correct?

Or else will you please send me step by step procedure to single ended operation.

Previously I raised some questions but nothing changed.

So please help me out with this.

int main(void)

{

volatile uint32_t i;

WDT_A->CTL = WDT_A_CTL_PW | // Stop watchdog timer

WDT_A_CTL_HOLD;

P2->DIR |= BIT0; // Set P2.0 CS1

P1->DIR |= BIT0; //CS2

P2->SEL0 = BIT1 | BIT2 | BIT3; // Set P2.1, P2.2, and P2.3 as

// SPI pins functionality

EUSCI_A1->CTLW0 |= EUSCI_A_CTLW0_SWRST; // Put eUSCI state machine in reset

EUSCI_A1->CTLW0 = EUSCI_A_CTLW0_SWRST | // Remain eUSCI state machine in reset

EUSCI_A_CTLW0_MST | // Set as SPI master

EUSCI_A_CTLW0_SYNC | // Set as synchronous mode

EUSCI_A_CTLW0_MSB; // Set clock polarity high

EUSCI_A1->CTLW0 &= ~EUSCI_A_CTLW0_CKPL;

EUSCI_A1->CTLW0 &= ~EUSCI_A_CTLW0_CKPH;

EUSCI_A1->CTLW0 |= EUSCI_A_CTLW0_SSEL__SMCLK; // ACLK

EUSCI_A1->BRW = 0x0001; // /2,fBitClock = fBRCLK/(UCBRx+1).

EUSCI_A1->CTLW0 &= ~EUSCI_A_CTLW0_SWRST;// Initialize USCI state machine

// Enable global interrupt

__enable_irq();

/***** DEV_ID***/

P2->OUT &= ~BIT0;

write(0x20);

write(0x00);

write(0x79);

write(0x00);

write(0x00);

write(0x00);

P2->OUT |= BIT0;

/****MODE-0***/

P2->OUT &= ~BIT0; // CS low

write(0x42);

write(0x24);

write(0x5A);

write(0x00);

P2->OUT |= BIT0;

//// /***** MODE-1 ***/

P2->OUT &= ~BIT0; // CS low

write(0x43);

write(0x01);

write(0xB4);

write(0x00);

P2->OUT |= BIT0;

/***** REF ****/

P2->OUT &= ~BIT0; // CS low

write(0x46);

write(0x10);

write(0x82);

write(0x00);

P2->OUT |= BIT0;

////

// /***** MODE - 4*********/

P1->OUT &= ~BIT0; // CS low

write(0x50);

write(0x33);

write(0x42);

write(0x00);

P1->OUT |= BIT0;

while(1)

{

/**** start ****/

P2->OUT &= ~BIT0;

write(0x08);

write(0x00);

write(0x7F);

write(0x00);

P2->OUT |= BIT0;

/********* RDATA *******/

P2->OUT &= ~BIT0; // CS low

write(0x12);

write(0x00);

write(0xAA);

write(0x00);

write(0x00);

write(0x00);

write(0x00);

write(0x00);

write(0x00);

P2->OUT |= BIT0;

/**** STOP******/

P2->OUT &= ~BIT0;

write(0x0A);

write(0x00);

write(0x55);

write(0x00);

P2->OUT |= BIT0;

}

}