Dear all,

I'm using an ADS5294 ADC in order to sample the output of an ASIC.

We need to sample stable DC levels generated by the ASIC output multiplexer (staircase)

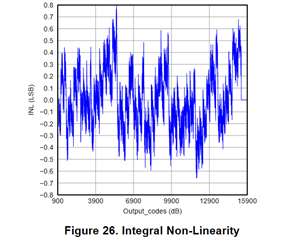

We are concerned about the non linearity of the ADC.

I connected the ADC to a Kintex7 FPGA and one of the 8 analog input is connected to a ramp generator that swing in the full dynamic of the ADC.

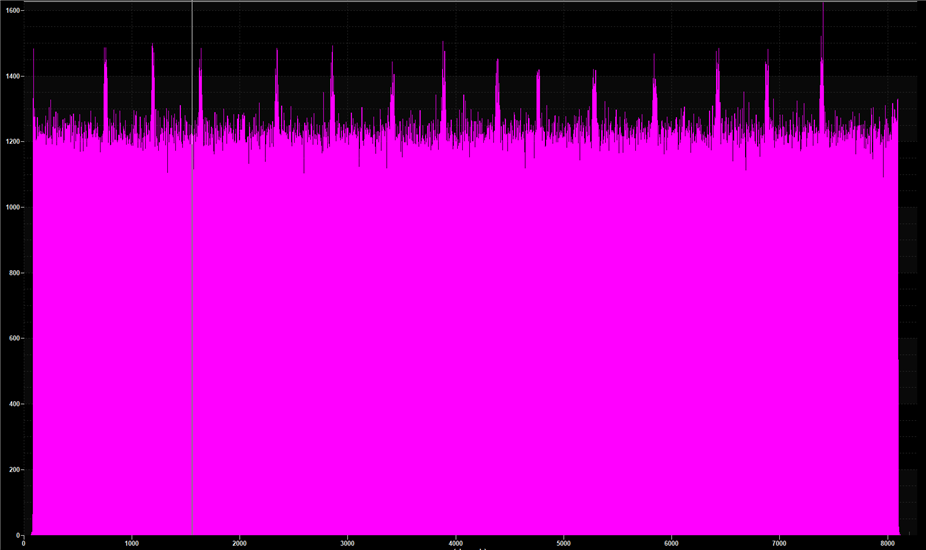

I have a true random pulse generator that trigger the FPGA to sample a point of the ramp and histogram it. In this way i should generate a white distribution.

I would expect a perfect white distribution but i got a distribution like this (with sever peaks)

The peaks positions are different for each channel of the ADC.

If i repeat this test enabling the digital ramp generator (and not sampling the analog signal) in the test pattern i got a pure white spectrum.

It look like that the INL of the ADC create these peaks but the effect seams to me too big to be acceptable; it is about the 15-20% of counts difference between baseline and peaks.

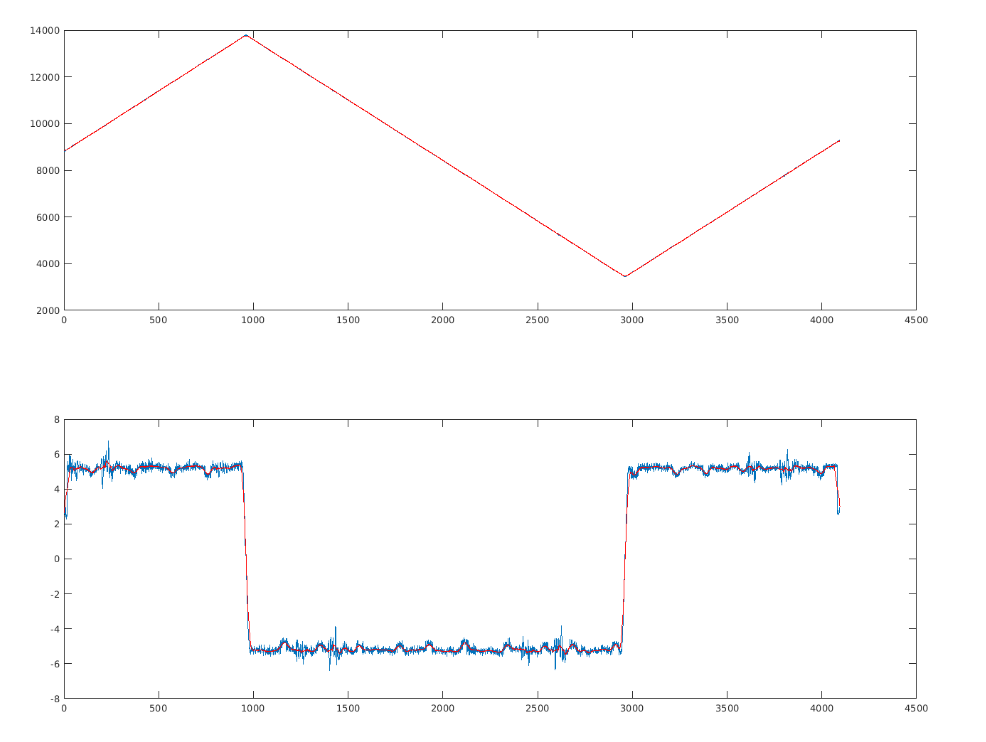

I investigated the signal shape. I sampled a ramp perdiod that swipe between 0 and full scale. I applied a moving average to reduce the noise (first plot) and calculated the first derivative (second plot) and its filtered version (red in second plot) and i see that the derivate is not linear, There are some humps and each one correspond to a peak in the histogram

Is this the normal behavior of this ADC or we should investigate for any problem on our board?

is there any way to reduce this effect? (hardware dithering is not possible)

Thank you

Andrea Abba