Dear all,

I am using 4DSP kit and in that I have TI ADC model ADS62p49.

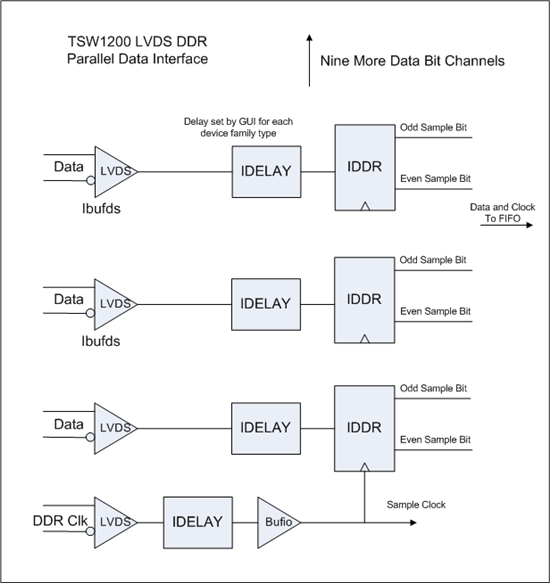

Now The thing is that I am using channel 'a' of ADC which uses LVDS differentail clock and I want to inqure that since I want to capture that data to the FIFO should I use the differential to single ended buffer like the following code

Note that there is a IP defined to capture the data words, all I have to do is to utilize it at my will, first step of which is storing to FIFO.

-- IBUFDS: Differential Input Buffer -- Virtex-6 -- Xilinx HDL Libraries Guide, version 13.2

IBUFDS_inst : IBUFDS generic map ( DIFF_TERM => FALSE, -- Differential Termination IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for refernced I/O standards IOSTANDARD => "DEFAULT") port map ( O => O, -- Buffer output I => I, -- Diff_p buffer input (connect directly to top-level port) IB => IB -- Diff_n buffer input (connect directly to top-level port) );

What I think this way I will be utilizing same clock both for Analog-to-Digital conversion and Data capturing to the FIFO.

What does the experience community fellows suggest. If there is any other better option please suggest.

Note: The FPGA is Virtex 6 and using ISE 13.2

Bests

Jaffry