Hi all,

The link below shows the default pin configuration over ADS1298 ECG FE, however when I connect the pins like that I cannot observe any signal on LCD. Moreover when I look at the DRDY I see a 3.3 V high voltage but not toggling. CS also seems high and SCLK is low.

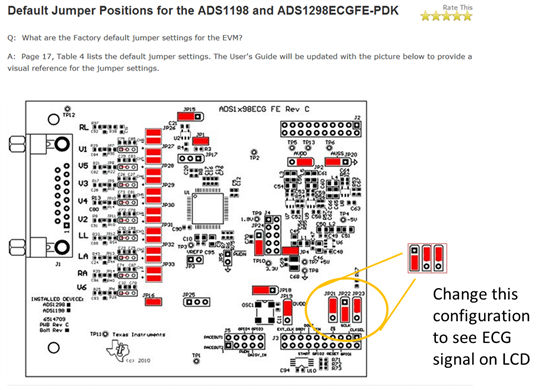

http://e2e.ti.com/support/data_converters/precision_data_converters/w/design_notes/1535.aspx

When I connect the jumpers like below, I see the signal on LCD after loading ECG_NonBios.out and all the signals DRDY, SCLK, CS are OK. Are there anything wrong? If not, then what is the confusion about default pin configuration.

For the configuration on the left (with ECG_NonBios.out loaded) I added the signals below:

By the way, when I build and load my code, I see the signal waveforms below , I couldn't be able to figure out the problem and need professional help:

Please, please, please help....

Regards...