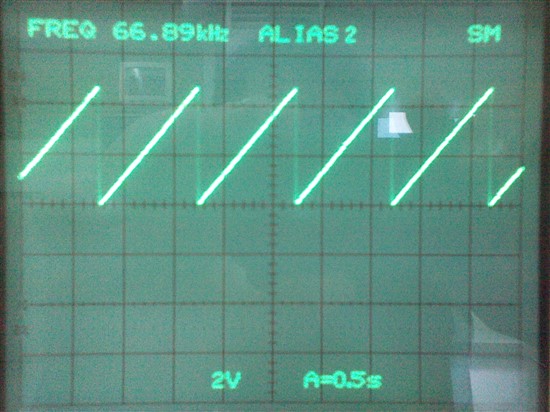

Hi everibody. Just trying to interface a 10 Bit serial DAC (SPI protocol) to a ordinary 8bit microcontroller. I have written the code in assembly and all the timing constraints are respected: However when I try to put a saw-tooth waveform at the DAC output I get the following result:

Where those glitches come from? They seems random, so they are some kind of noise however their amplitude is too high to be conversion noise. The error seems normally distributed...

Please note that the DAC update is 2MHz, way below his maximum value, and the signal generated has a period around 2KHz.

Any help toward the understanding of this effect will be appreciated.

Best regards to all.