Other Parts Discussed in Thread: MSP430F5438, ADS1248, ADS1246

Hello, I'm trying to run an ADS1248 following the example on page 55 of the device datasheet. The only difference is that I'm doing it with 3 channels. I'm trying to do this with a MSP430F5438. I attach a picture with the schematic. I know that it isn't a hardware problem, because I run it with different configurations, but this is the configuration I need for my application.

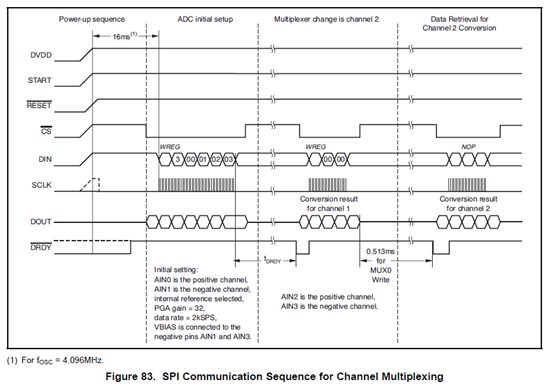

First of all, I make the initialization of the MSP, initializing the LFXT1 at 8MHz and the series port. Then I start my code following the Figure 83 of the ADS1248 datasheet (Figure 83. SPI Communication Sequence for Channel Multiplexing).

I'm going to explain my code, because I think that I'm making a mistake in the process.

First off all, I make an initialization of the SPI that communicates with the AD. I put a frequency of 1MHz. I also configure the port P1,7 as a Lo/Hi interrupt. I put the Sart, Cs and Reset pins at high value (CS and reset are active at low state, so I put a 0 on them). Then I make a delay of 2^16 cycles and then I put the CS on low state.

After this, I start the configuration of the registers of the AD.

First of all, I send the WREG command, 0100 0000 indicating that the address of the first register to read is 0. Then I read and discard the answer of the AD. Then I send an 0B, indicating that I'm going to write in 12 registers. I continue sending the values of the registers and reading the answer of the AD. When this finishes I put the CS to high state.

Then in the main program I wait until DRDY goes from Lo/Hi, when this happens I put the CS to low state and I start reading and discarding the first value. Then I send WREG in order to indicate that I want to change the channel I'm using . I use the first to sends to send the WREG values. Meanwhile I save the first two values of the conversion (MSB and the middle value). Then I send the value of the following channel (If I had read CH0, now I say that I want CH1, if I'm in CH1, I say CH2, and if I'm in CH2 I return to CH0). After saing the value of the register MUX0 I read the LSB of the conversion. Then I put the CS to high state and I returnto wait the DRDY signal.

Sorry if there is any spelling mistake. Can somebody help me with this? If it is necessary I can put my code here.

Also a Code of the implementation on this diagram with some MSP can be very helpful for my project.

Best regards.