I am having a problem with the TLV2544Q 12-Bit Serial ADC. The LSB of the conversion result is always 0 when the measured voltage is at the higher end of the measurement range. Consequently, the ADC acts properly as a 12 bit ADC at low voltages and as an 11 bit ADC at voltages in the upper half of its range.

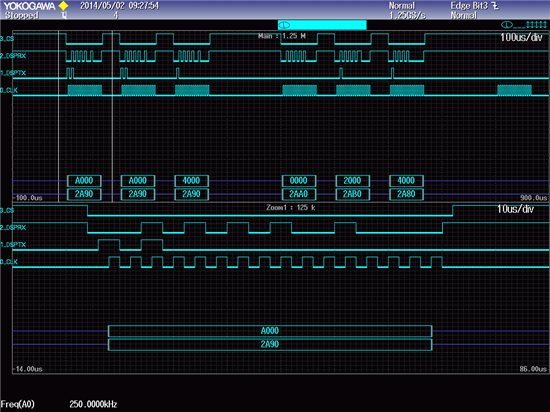

This problem was verified by inspecting the SPI signals directly.

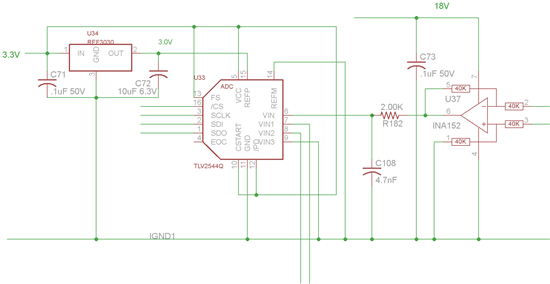

The ADC chip is wired and configured to use conversion mode 00 as shown on p 14 Figure 8 of the datasheet. The ADC chip is connected as follows:

VCC, PWDN, CSTART and FS to 3.3V

REFP connected to 3V dc

EOC not connected

GND, REFM and VIN3 connected to GND

VIN, VIN1 & VIN2 are the measured voltages

SCLK, SDI, SDO and CS are connected to a microprocessor

SCLK frequency is 635 kHz

The chip select goes true (low) 4us before the first rising edge of serial clock and false (high) 4us after the last rising edge of the serial clock.

What would cause the LSB to stay at zero?