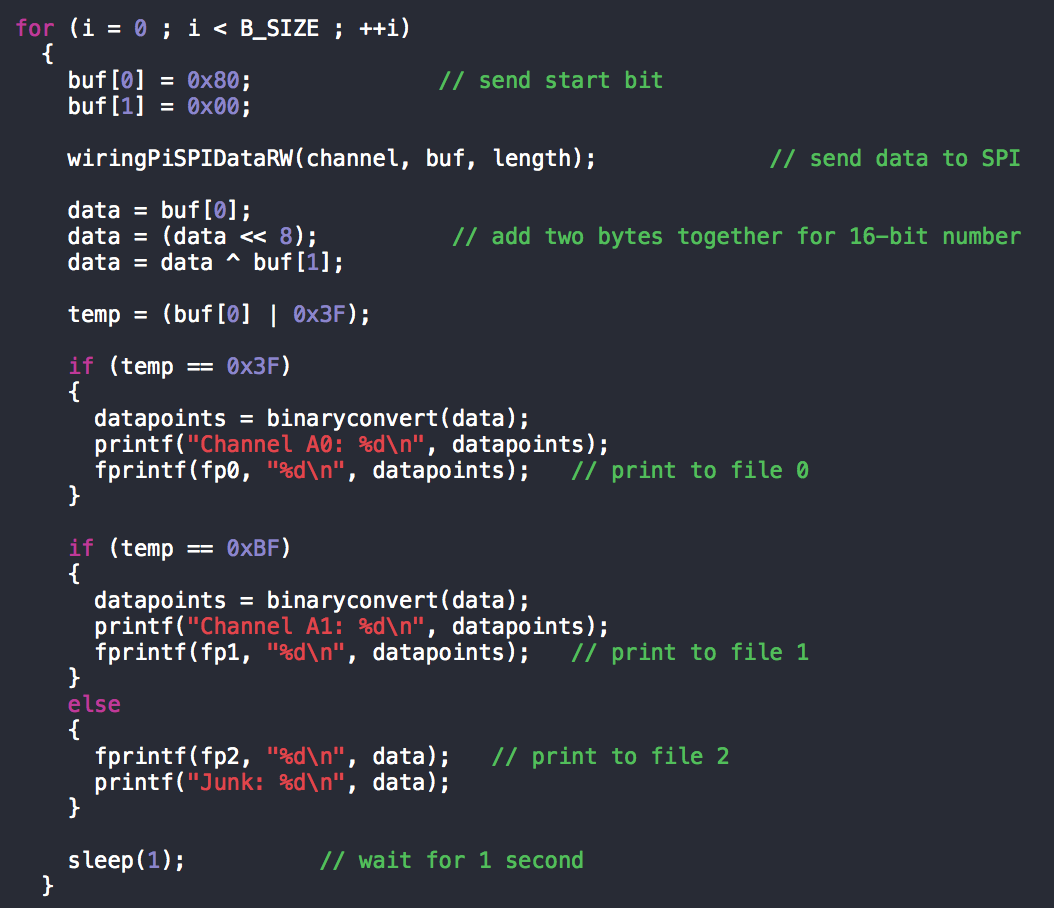

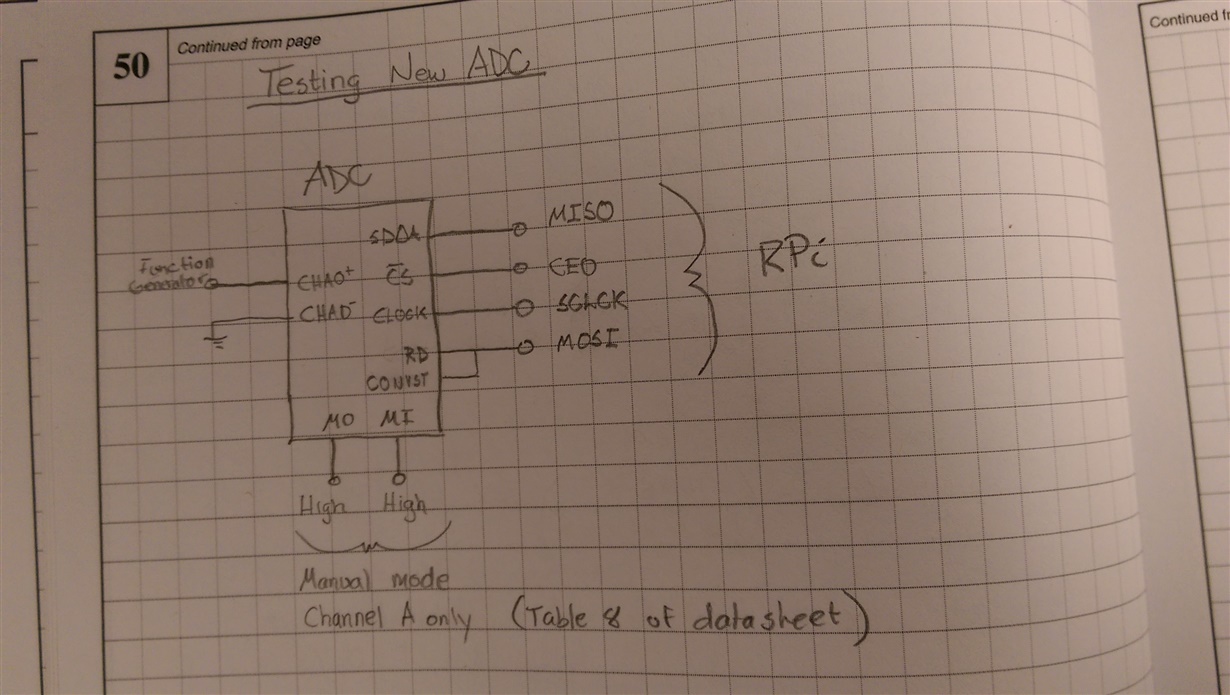

Is there anyway for this to work? All of the library's that I have tried to use (WiringPi, etc.) are configured for 4-wire SPI and not for the extra CONVST and RD wire. Is there a way to code around this, i.e., somehow connect the clock to another pin. Thanks!

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.