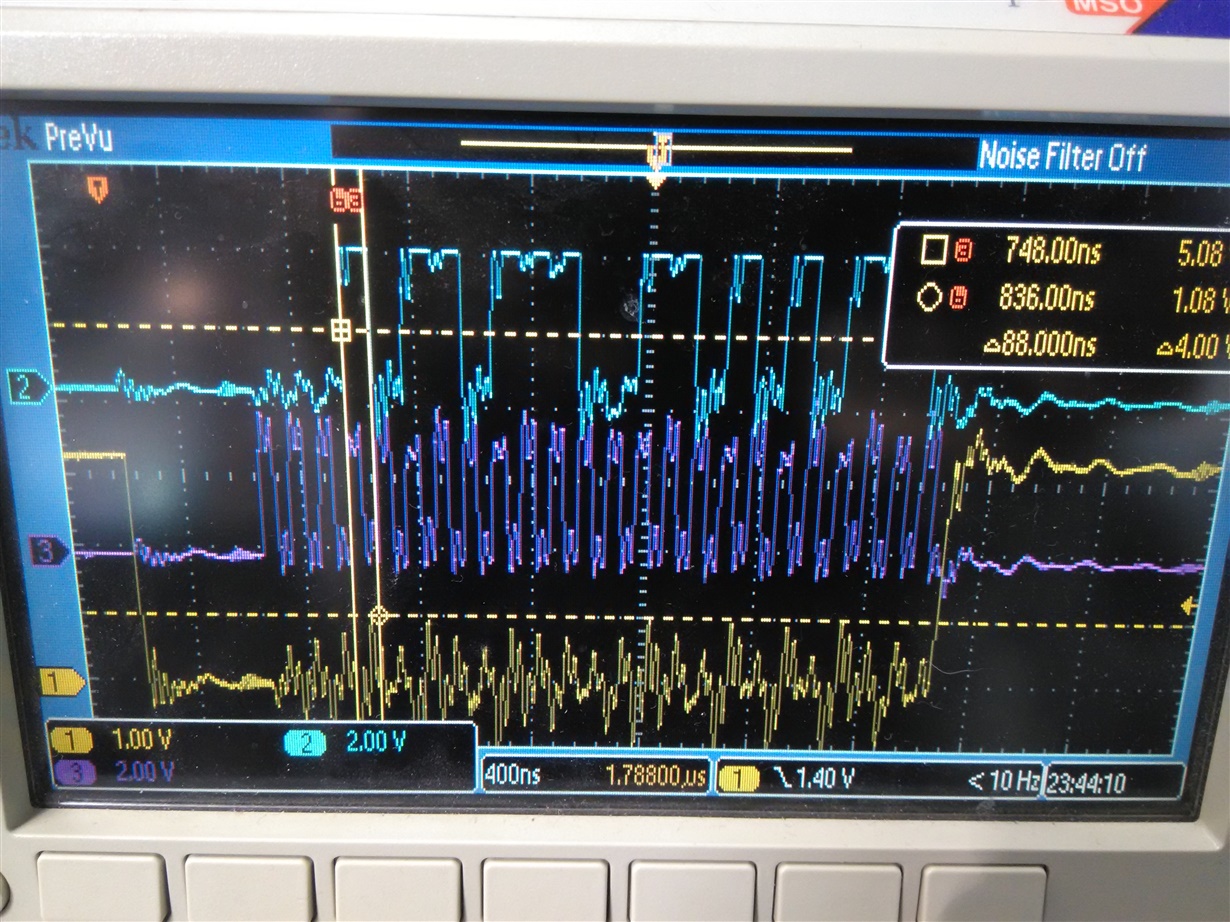

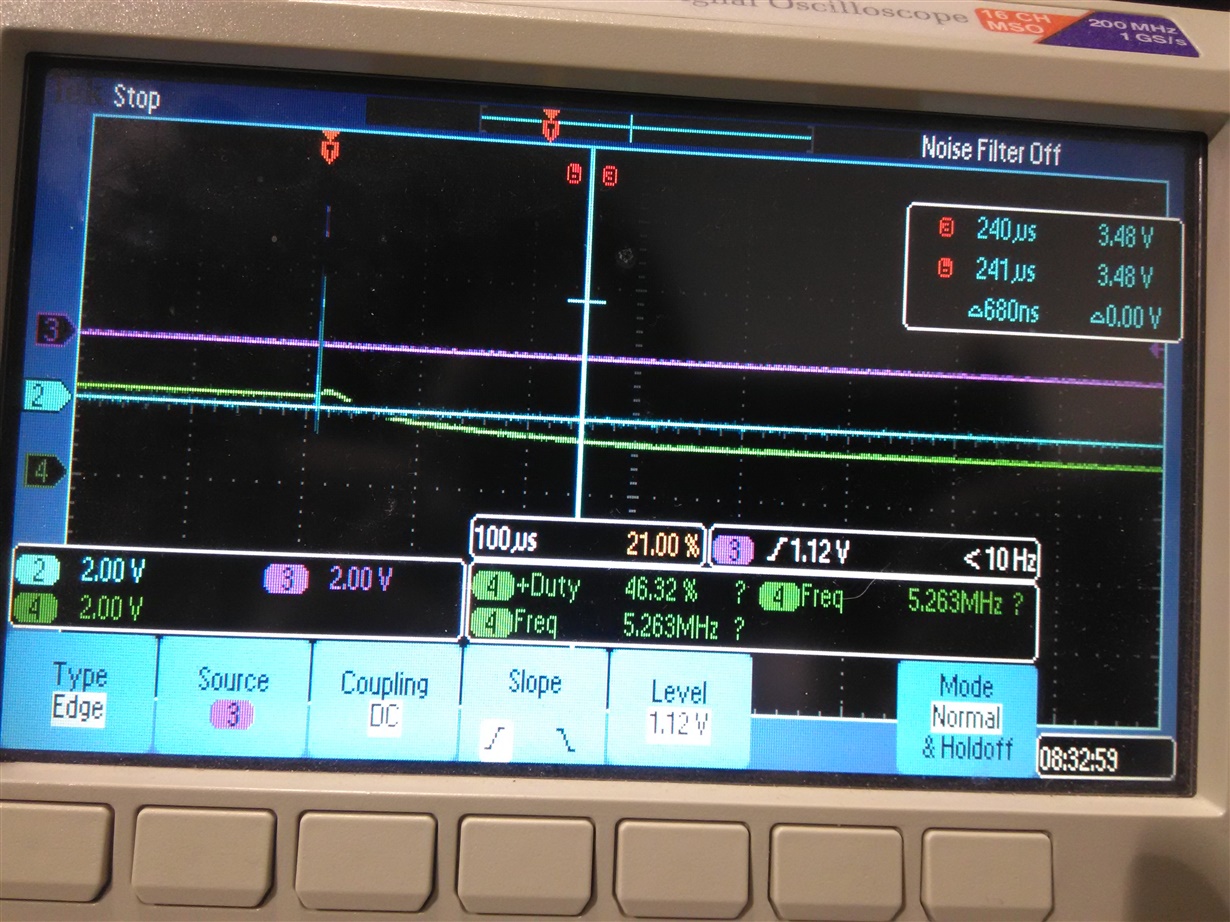

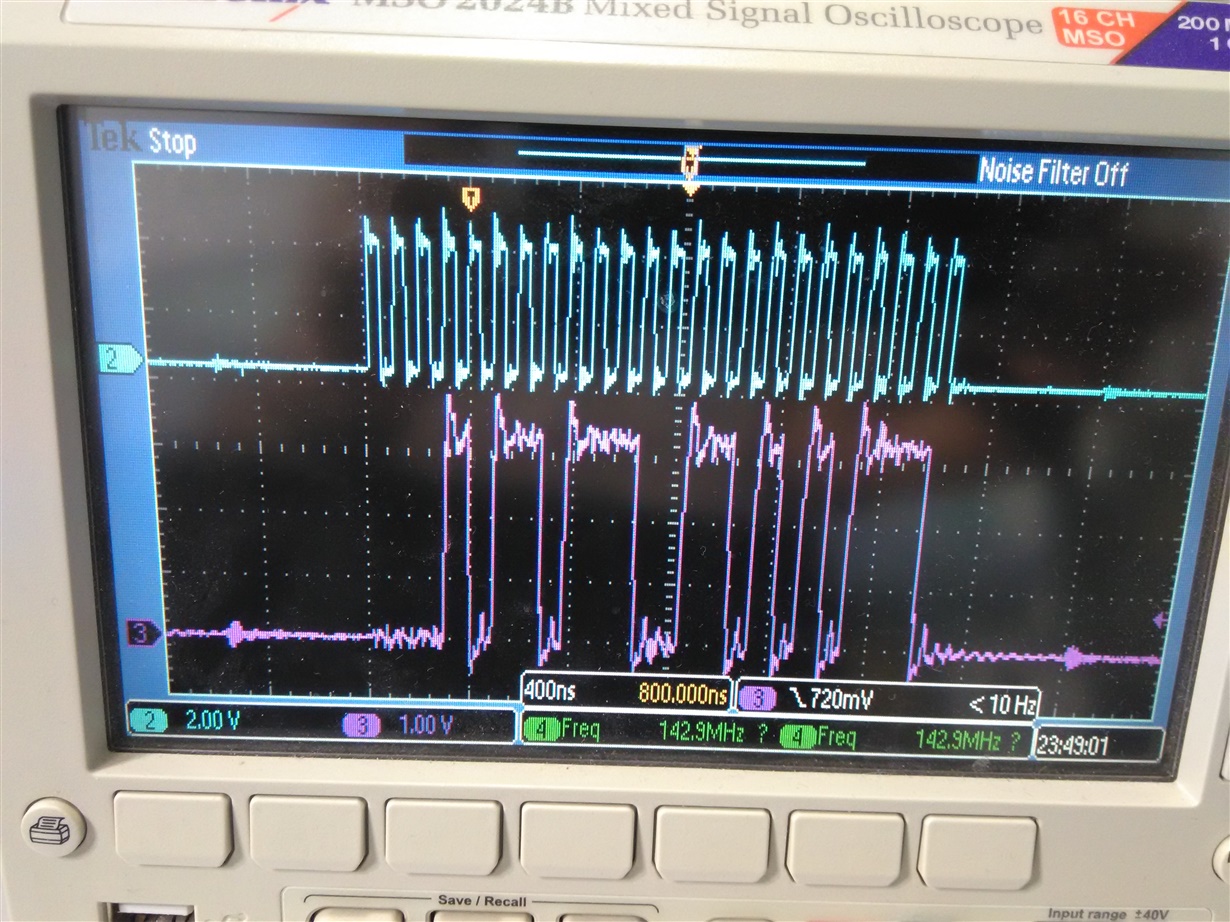

I am trying to communicate with DAC8564. My SPI speed is 16MHz, supply voltage is 3.3V. I have 4 DAC8564 IC's on a single SYNCbar line. Enable and LDAC pins are tied to ground. The internal regulator generates correct Vref of 2.5V on powerup. However as soon as I write data to it, the Vref collapses to 1.5V. I am not using external regulator. I am not sending power down command. What am I doing wrong?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.