Hello everyone.

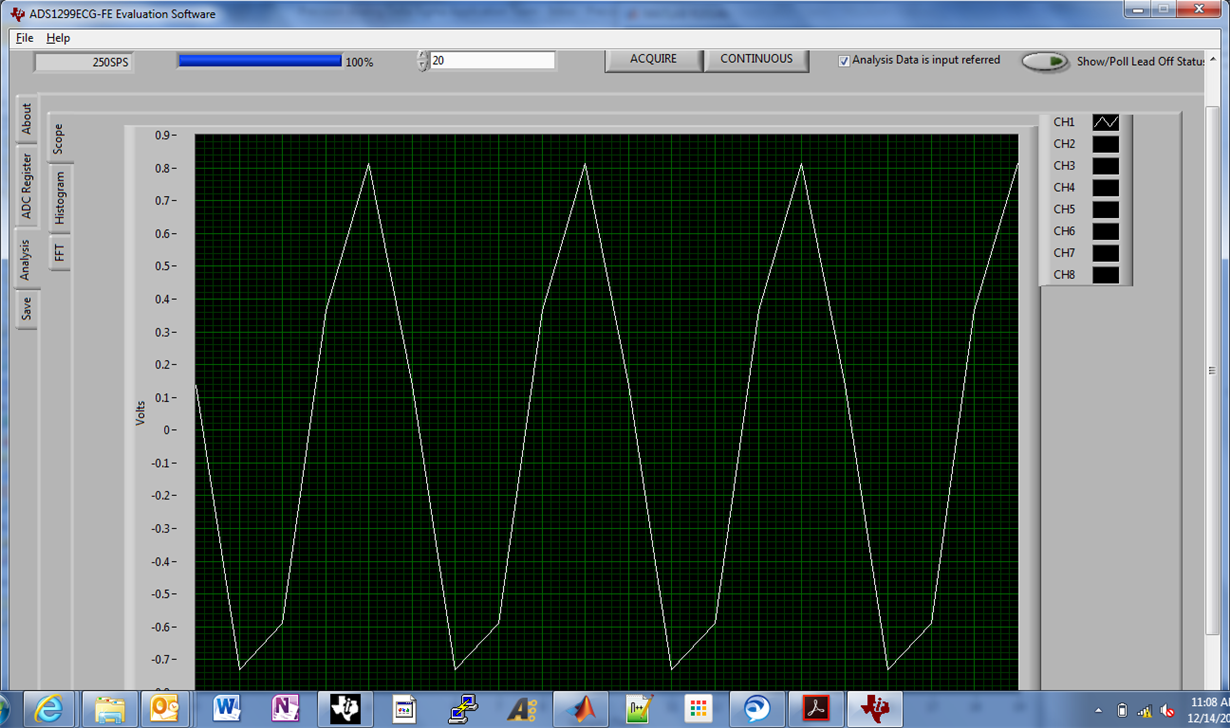

I have been working with an ADS1299 design quite successfully so far - until I finalized the evaluation process for faster biosignals:

Measuring the Frequency response of the system, I found an unknown low-pass source cutting off the signal way too early (-3dB @~50Hz).

I did manual sine source input and a frequency sweep analysis, both with the same results.

The only design elements between electrode input and ADS1299 IN1-8P/N Inputs are passive RC Lowpasses with a cutoff of ~530Hz (3kOhm|100nF) for each input. Negative inputs are shorted to one common input RC with the same values and one common electrode. All R/C elements were manually re-checked.

I use a samplerate of 500Hz which - according to datasheet - should lead to a ~130Hz input bandwidth of the chip - still way above the measured 50Hz.

This means that from 1-100 Hz the frequency response is neither completely flat, nor linear!?:

EEG Example: In Alpha (8-13 Hz) the attenuation already differs around about 8%. (8hz: 0% - 13Hz: 8%).

This can not be a characteristic of the ADS1299, can it?

I would be glad to get some information on possible sources for this behaviour - and upload the sweep-data and a snippet of the analog design for your convenience (unfortunately I did not find a way of doing this with the forum mask so far).

Thank you for any ideas or reports of similar issues!

Alex