Hi,

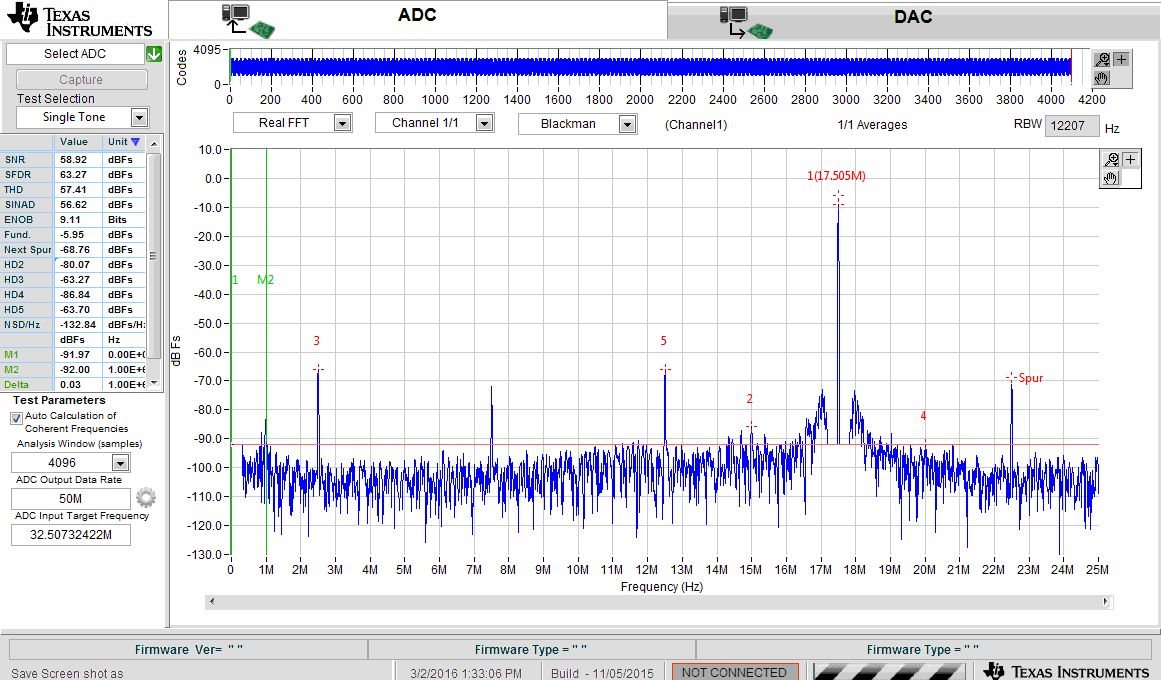

We are using ADS61B29 at 50MSPS in our board. We are feeding a input of 32.5MHz at -6dBFS. When we capture the digital data and plot it in wavevision, we are seeing a unexpected degradation in SFDR and ENOB. We are seeing the harmonics with considerable amplitude as shown the FFT below:

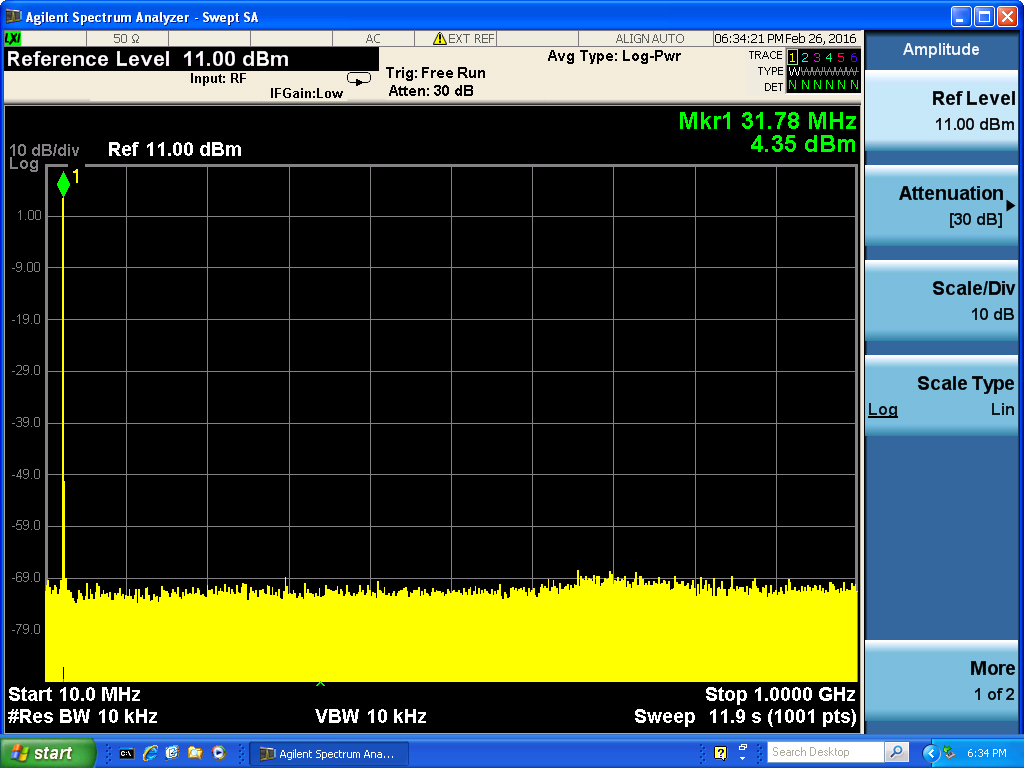

The input signal fed to ADC is analyzed using spectrum analyzer and screenshot is shown below:

The following figure is the FFT of digital data when ADC input is terminated with 50ohms:

Please help us to proceed further. What could be the problem for this?

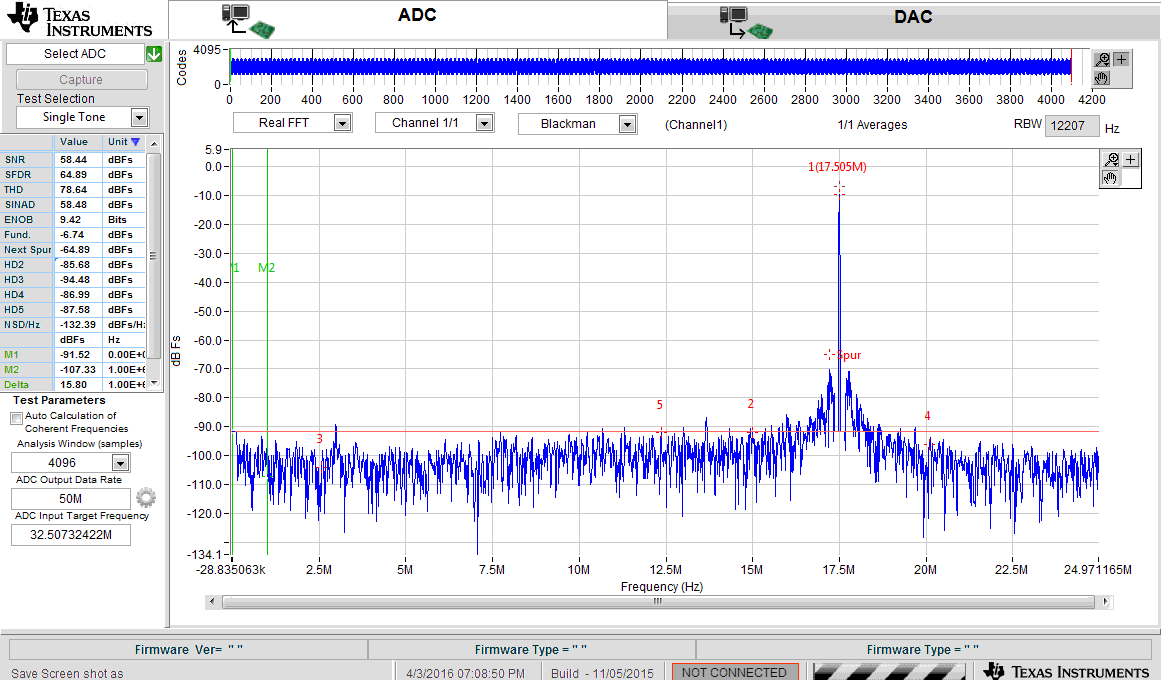

Edit 1: HSDC Pro screenshot also included. :

Edit 2:

We were using on board oscillator generated clock. Changed to external clock and captured. The plot is :

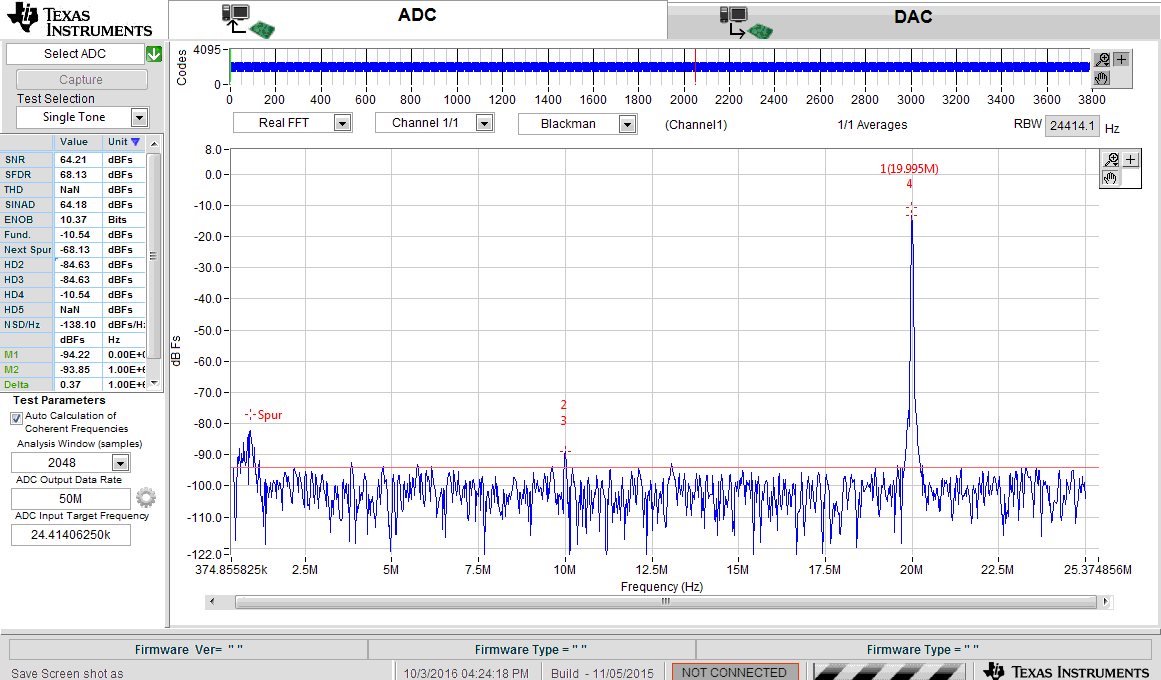

Edit 3:

Signal source is changed to R&S signal generator as suggested by Richard :