Hello,

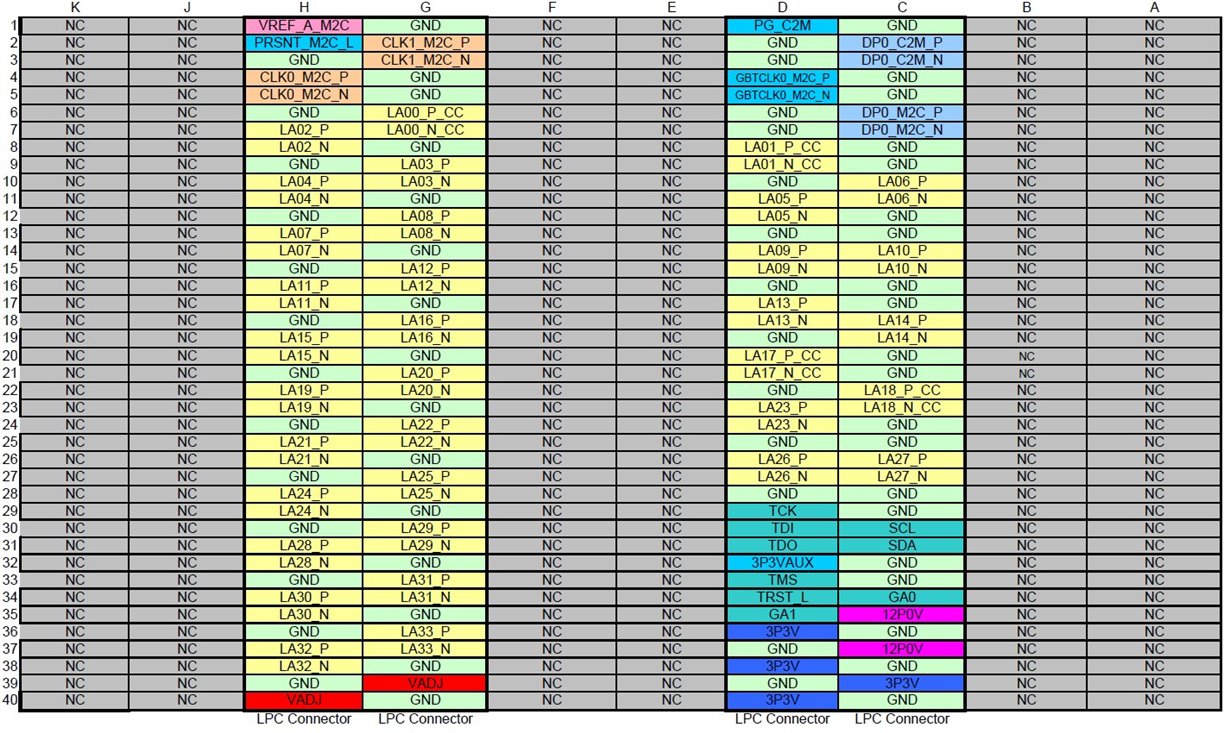

With regards to the ADS54J54EVM ADC Evaluation Module, I've noticed that on the provided design package on the schematic file, the FMC pins seem not to be wired according to the LPC configuration (currently our development is on the Avnet Kintex-7 Mini-Module Plus board, with banks CDGH wired into the FPGA as per LPC).

Is the schematic accurate, and if so, are there ways (i.e. boards, connectors) that can adapt the current ADS54J54EVM FMC pin configuration into ones that comply with LPC?

Thank you.