Hello,

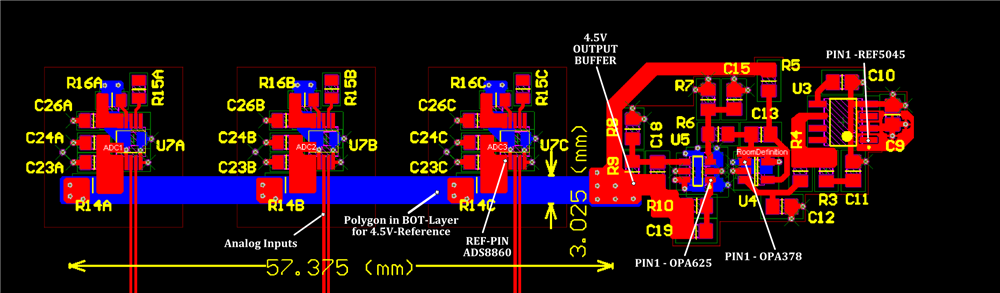

Regarding the composite buffer you proposed here, could you please take a look at the layout for the composite buffer (OPA378+OPA625) and the connection of the 4.5V reference voltage to the ADS8860.

I'm using a 4-Layer PCB (Signal/GND/Power/Signal). For space reasons I was not able to put the output of the composite buffer closer to the reference input-pin of all the ADS8860. I used for this a polygon on the bottom layer and then I connect this signal to the top layer using vias (0.3mm/0.6mm) to another polygon connected to a resistor (R14 / 0.22Ohms) in series with the local capacitor (C23 / 10uF).

I would appreciate your thoughts on this.

Thank you and kind regards,

Sebastian