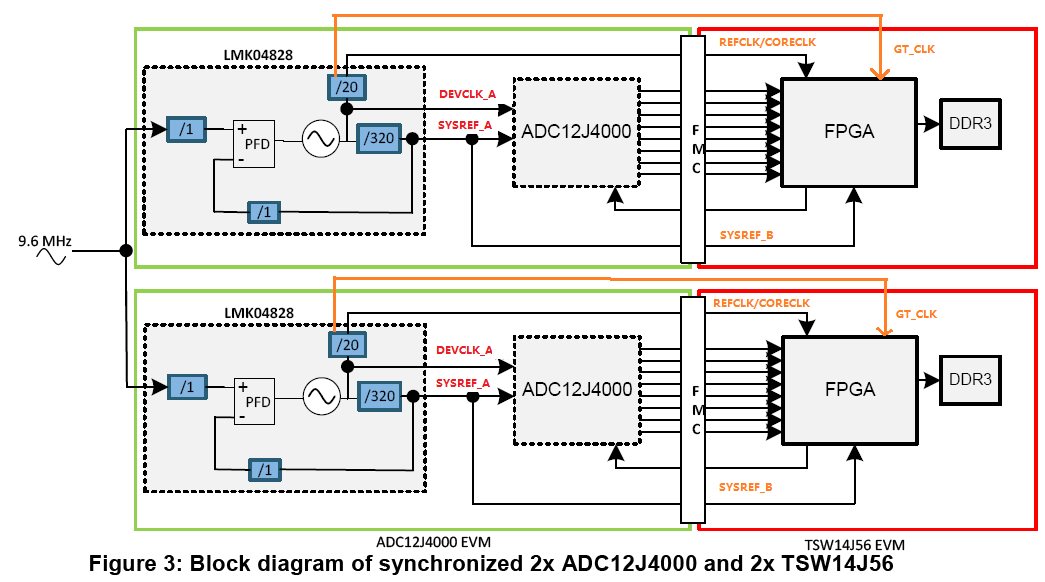

I recently learned how to use the Jesd204 ADCs,there is a example design Synchronizing Multiple ADC12J4000 ADCs 'tidu851'.

I have some questions about Jesd204B-1 clock configuration:

1.about LMK04828:

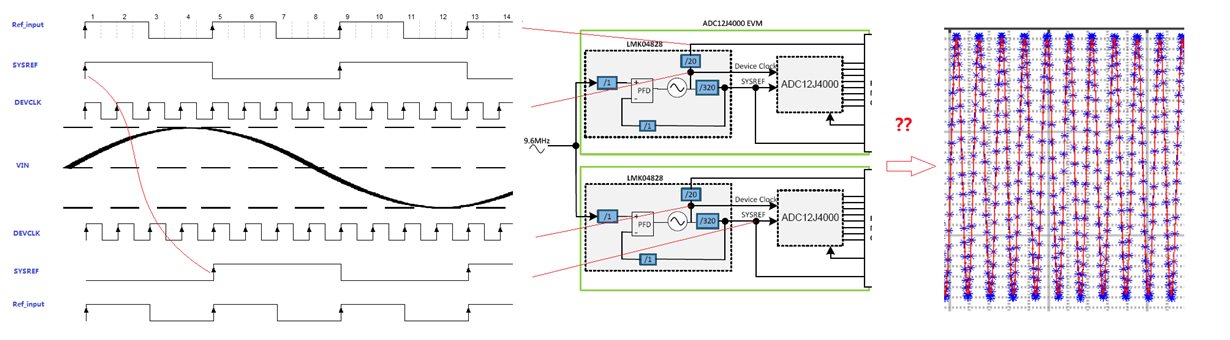

'SYSREF_A' and 'DEVCLK_A' on each ADC12J4000 EVM should be phase aligned,so a common SYNC must be posted to each LMK04828 'SYNC/SYSREF_REQ' input on each ADC12J400 EVM? but i see no such wire connection.

2.about FPGA device clock:

FPGA Jesd204B RX need a 'refclk' and 'glbclk' which corresponding to 'GTX reference clock' and 'core clock',does 'refclk' and 'glbclk' must all be phase aligned(core clock is needed when core clock is greater than 165MHz or not equal to reference clock)?