Other Parts Discussed in Thread: REF5045, OPA625, , OPA378, THS4551

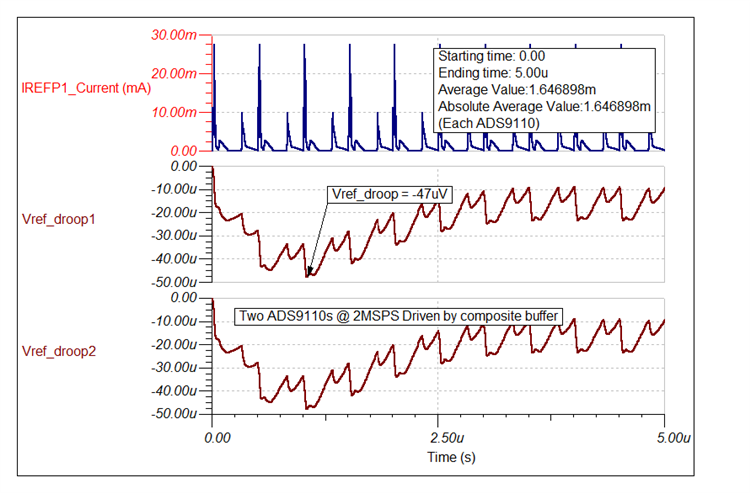

Hi, I am using 24 of ADS9110 ADCs on a board and would like to provide a common 4.5V reference to all (if not one for 12 devices). I'm planning follow the design based on REF5045 and OPA625 that is provided in the datasheet and provide 3 x 10 uF capacitors per ADC. The design is to be used at 2MHz sampling and I still want to achieve performance within 1LSB (3.8ppm x 4.5V = 17uV).

Can you please advice me if the reference circuit provided in the datasheet can reliabley work on this arrangement?

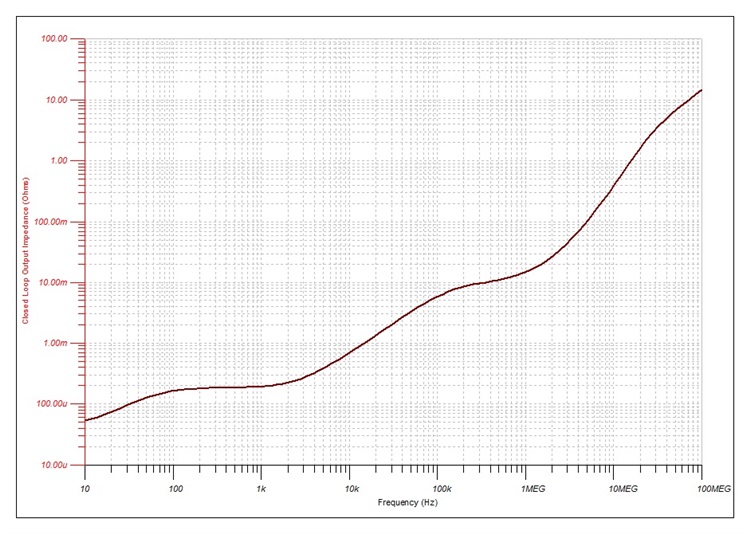

I have used TINA and simulated the reference circuit (REF5045+OPA378+OPA625) with 360uF capacitive load. I used a Iload of 15mA @ 2MHz and the ripple is about 21uV (approx.). Is this 15mA @ 2MHz an overhill to test the circuit? Is thts 2MHz the representation of CONVERION (i.e, the rate at witch the Iref is drawn)?

I am in the process of finalising the schematics and cannot make up my mind on this. The design is pused to give the optimum SNR and dynamic range.

I also want to have a separate buffer attached to the same reference IC REF5045 to generate VOCM (2.25V) for 24 sets of THS4551 fully differential amplifiers. Is this allowed or should I implement a separate circuit to avoild possible glitches?

I have included the TINA circuit that I simulated.

Thanks

Regards

Billy