Other Parts Discussed in Thread: TMS320F28335

Hi

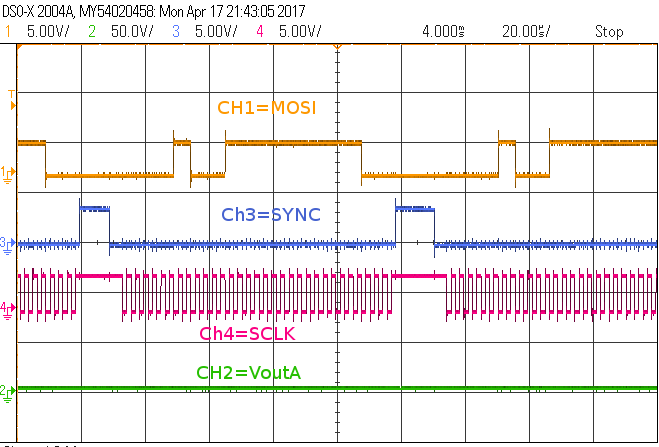

I have been trying to use DAC60004 with SPI communication using TMS320F28335. The SPI part of the code is working well. But the DAC output is always zero. I have tied LDAC(pin1) to zero and CLR (pin9) to VDD. The REFIN(pin7) and POR(pin6) are both connected to VDD (pin3). SCLK from dsp to pin 14 and MOSI from dsp to pin 13. The SPISTEA signal of dsp is used as SYNC (pin 2). The command given is 0x030FFFF0h- (command-write to buffer and update DAC n/ Channel A/DAC data FFFF). The SPI inputs to the IC is captured and attached with. I have a doubt regarding the dac data to be send. Though the DAC60004 is 12 bit, I suppose if FFFF is send from MOSI, the DAC should ignore the bits from D07-D04, so that the mode bits is always from D03-D00. Correct me if I am wrong. Also Is there a mistake in tying the LDAC to GND with the command given as write to buffer and update DAC n (D27-D24=3)? Could anyone help me out with this?

Regards

Deepthi