Part Number: ADC3422EVM

Hi All,

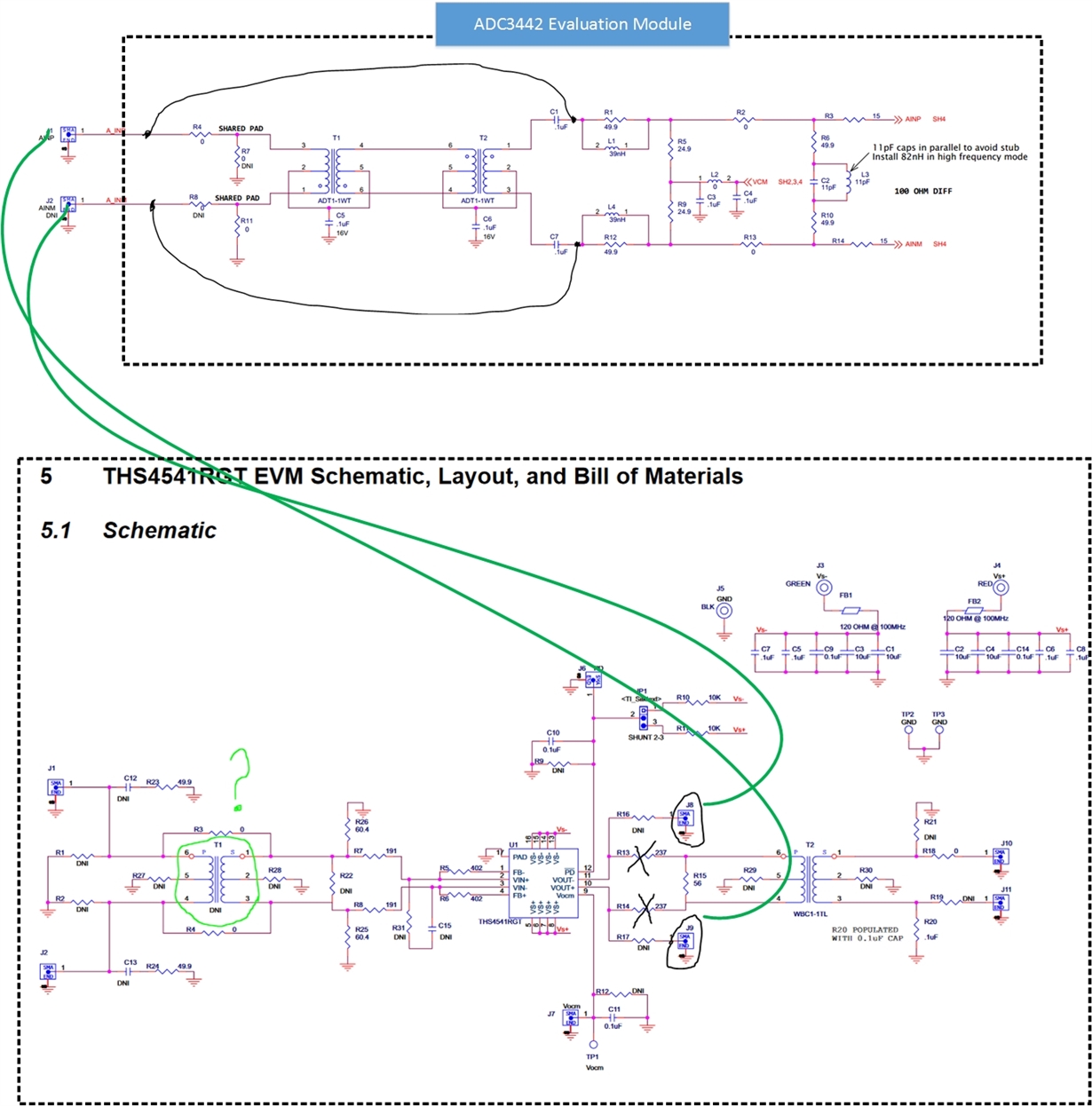

we are interested in ADC Evaluation Modules ADC3442EVM, ADS6422EVM, and ADC3423EVM. However, we have some simple technical questions to confirm our choices are correct for our application. I was wondering if you let us know the answer of the following questions:

- I saw TI uses 1:1 transformer for each analog input pin to have ac coupling. However, our analog signal is not a pure ac signal and has a dc bias which varies during time. So are our choices right for this application? In other words, does putting transformers in the path of analog signals impose any constrain for analog signals we can convert? for example, just pure high frequency ac signals can be converted by this evaluation kit.

- In order to capture the output digital converted data, we are using FPGA (Zedboard), which its input banks are compatible with LVCMOS data type. So we need to use ICs to converter LVDS data to LVCMOS, Is there any other option?

- And the last question is that: considering conversion time, serializing the data, and capturing it inside the FPGA, what should be the minimum sampling rate of ADC if we want to have the data inside FPGA after 800 ns from start of conversion command?

Thank you