Other Parts Discussed in Thread: ADS1013

I'm not quite understanding full scale range and its bearing upon differential versus single-ended mode for the ADS1014.

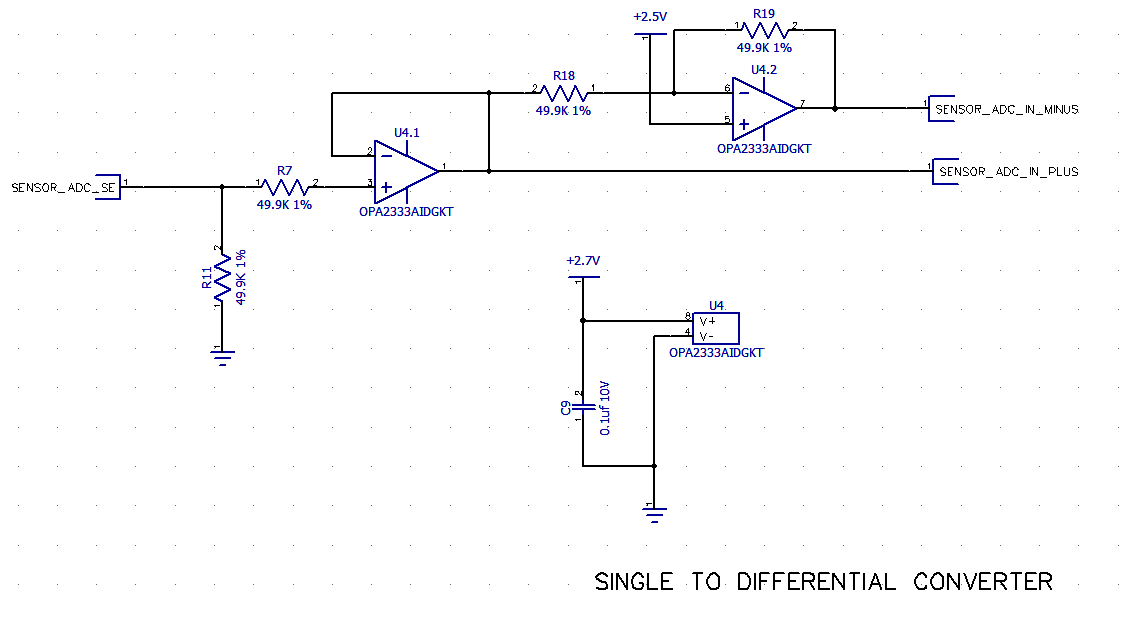

1) Full scale range is specified as +/- n volts. However we cannot go below the supply voltage ground reference. So, is FSR applicable to differential mode only?

2) The high range +/- 6.144V has a 3mV resolution. If I consider +/- 6.144V to mean a span of 12.288V, then 12.288/.003 == 4096 bits, and we use them all. However, as we cannot go negative, what then does +/- 6.144 mean? Perhaps differential mode allows the full span of each range to be used?

3) In single-ended mode do we connect AIN1 to GND? I don't see any advantage to put a positive bias on AIN1.

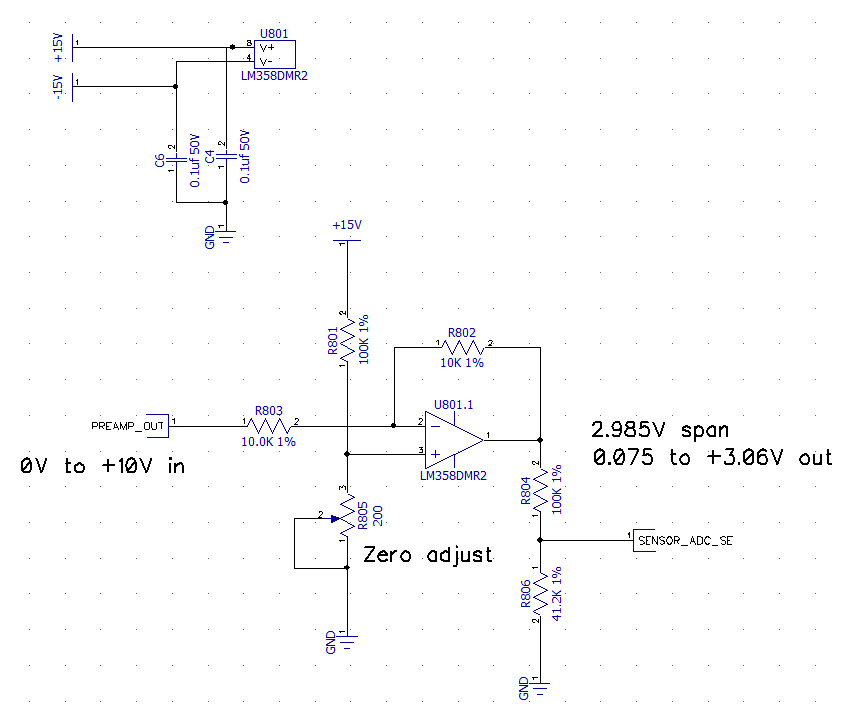

Our practical problem is this: we need to measure a sensor that tracks from -0.2v to +10V. Starting with a +/- 0.256V FSR, will changing the range as the signal rises be a good option? For a jellybean 10 bit ADC (+3V) we've processed the signal so the sensor voltage span translates from 0 to 3V. In doing so we lose quite a lot of resolution. Perhaps the ADS1014 offers us a better way?