hi Team,

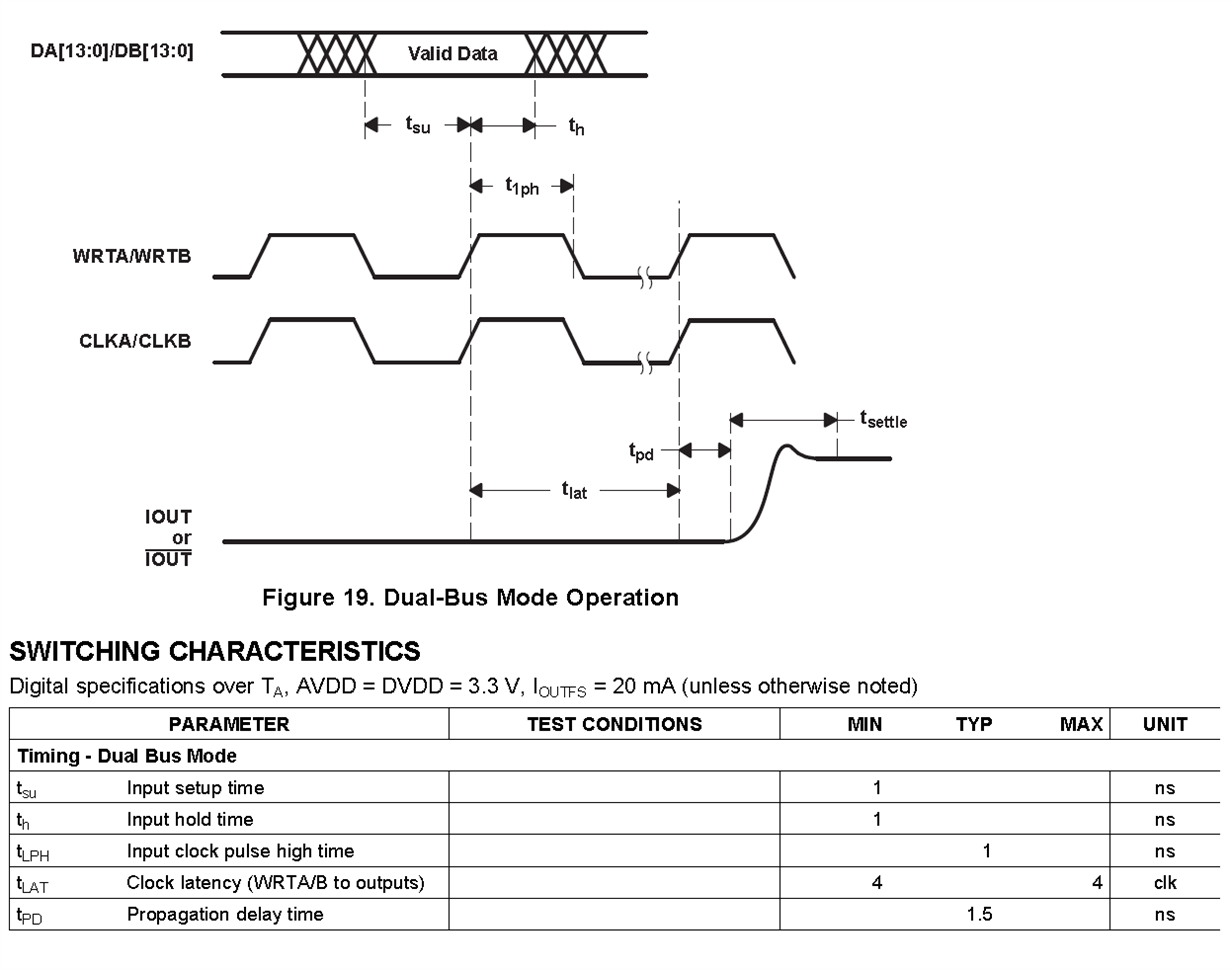

Customer want to understand a bit more about DAC5672A digital timing

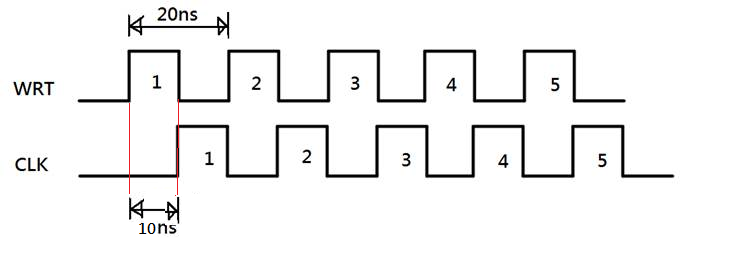

If customer is doing dual bus mode and they didn't short the WRTA/B and CLK in hardware, and they plan to fix it by software through FPGA. What they do currently is rising the WRTA/B pulse first then rising CLK as second. And they try to keep them apart by 2nS minimum.

Questions:

(1) Is Tsu and Th spec referring to WRTA/WRTB. (not short WRT and CLK)

(2) Datasheet said keep WRT & CLK apart by 2nS minimum. we don't have maximum spec?

(3) Is below digital timing works at all?

Thanks.

Regards,

Andrew