Other Parts Discussed in Thread: OPA320

Hi ,

I am Rahul from WT microelectronics.

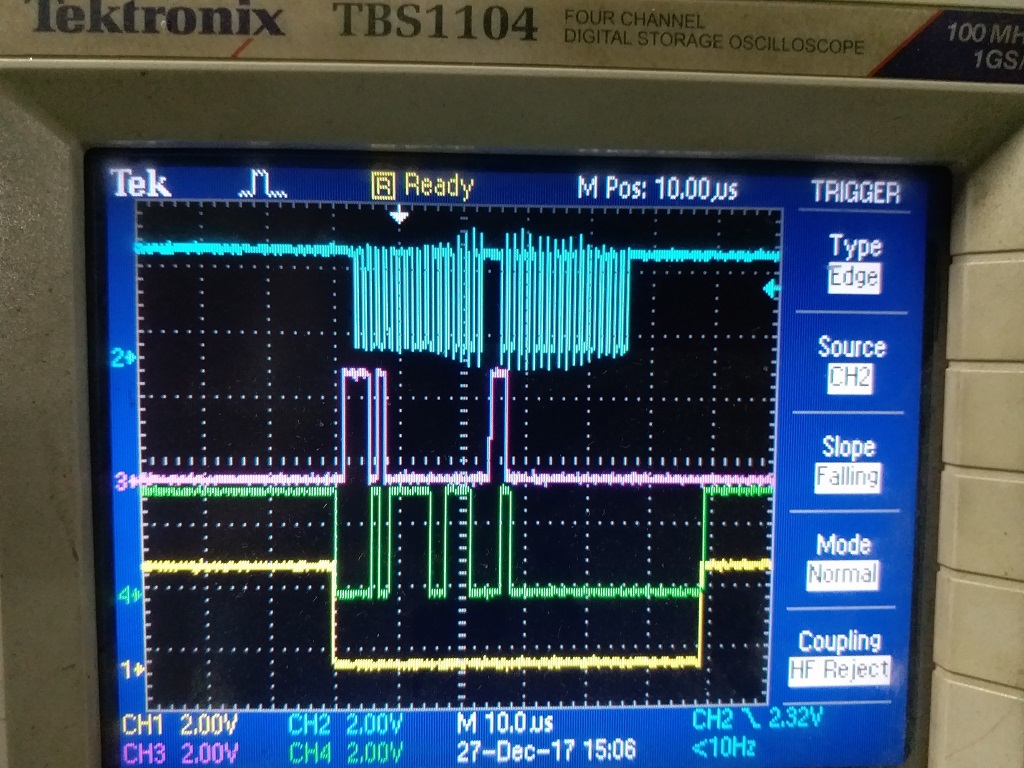

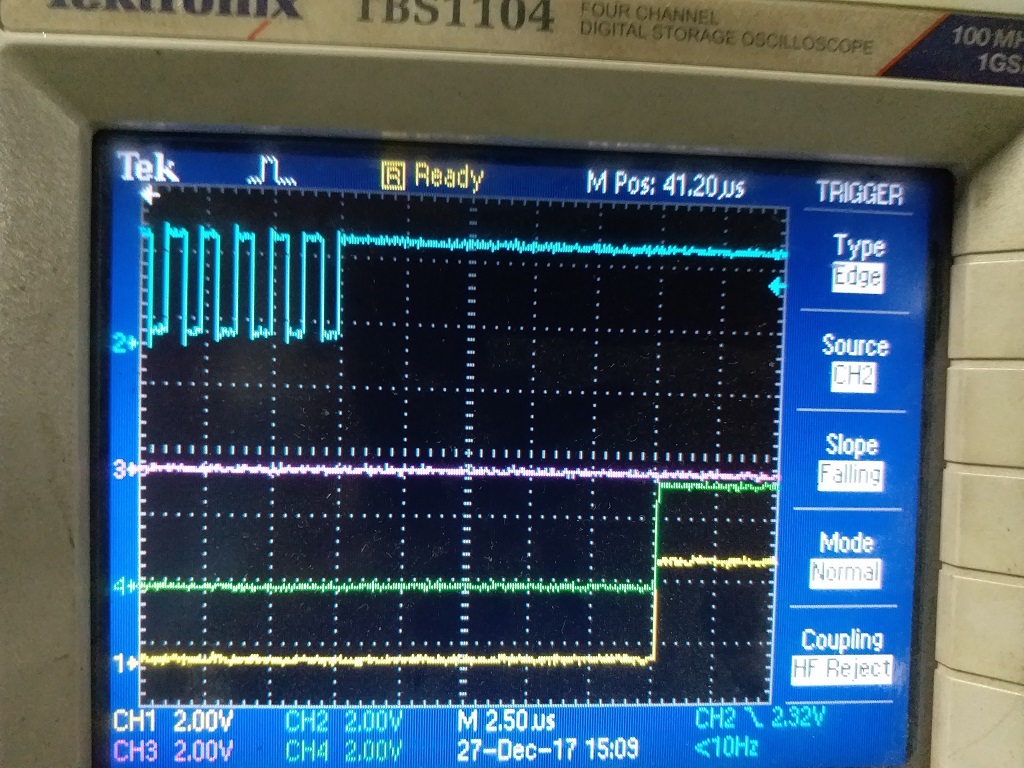

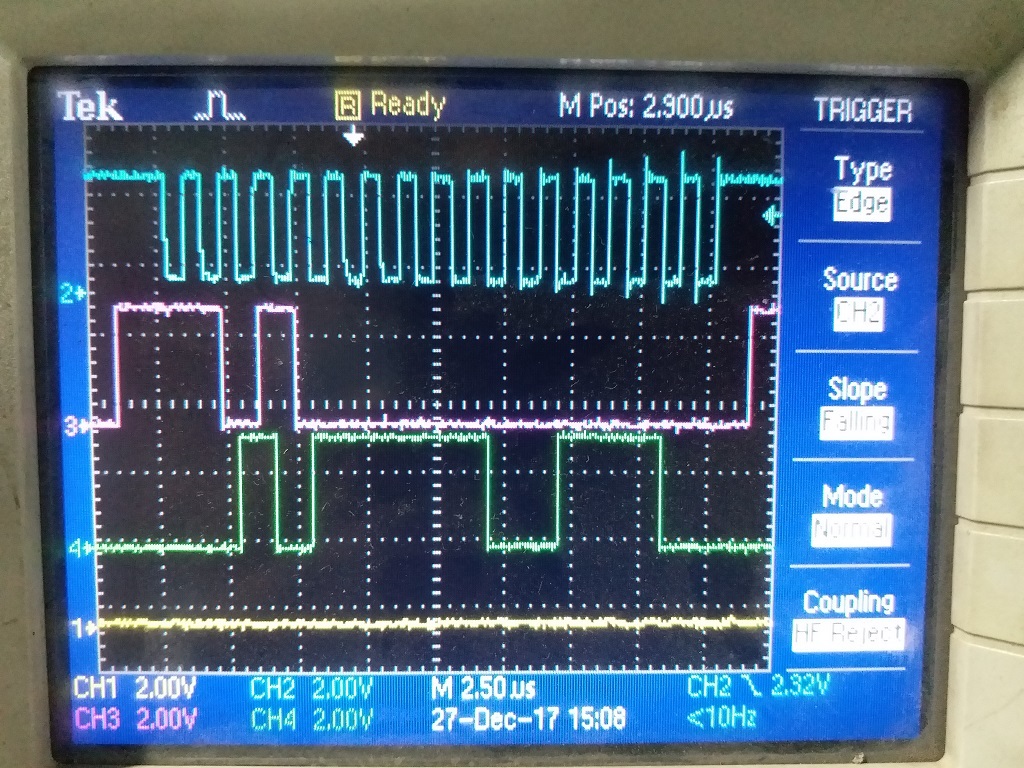

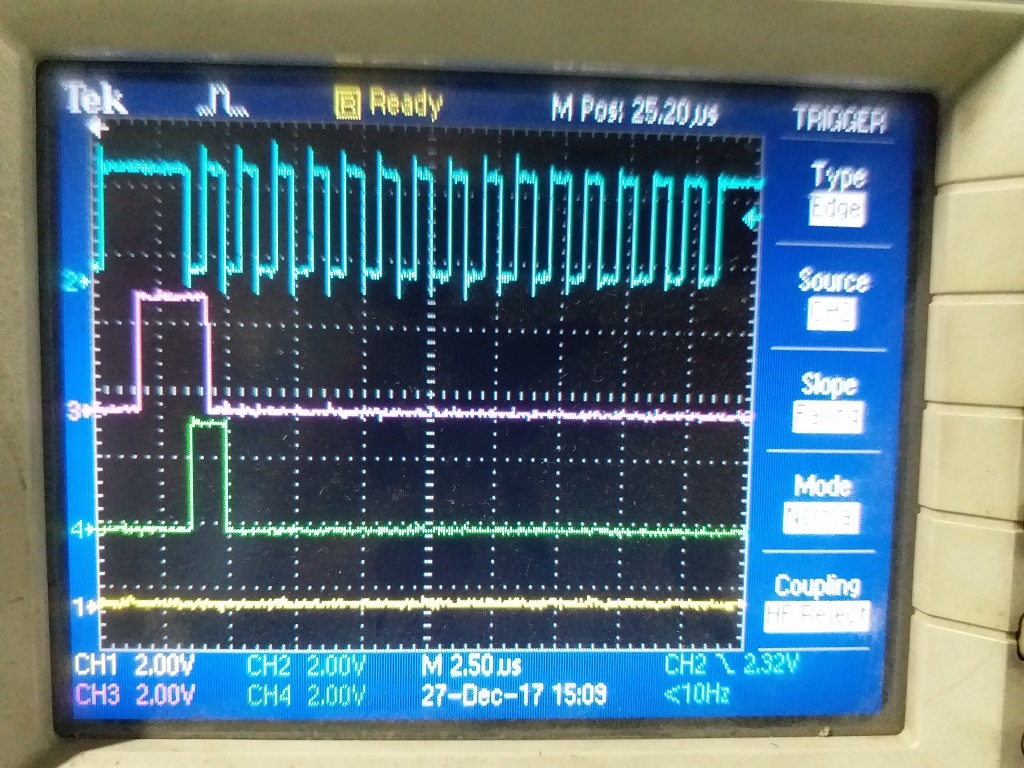

One of my customer using ADC8331 and communicate with MCU through SPI.

Issue is that data received by ADC is not correct.

Please check below

Data received.= 0X17CE(6094)

TAG BITS= 0b0100000000000000

but pin voltage is 2.462V @ channel no. 2.

Vref = 4.105V

CFR= 110011111111

packet to read data = 0b1101000000000000

Dummy to receive tag bits = 0b1000000000000000

in images

blue is clock

yellow is Chip select

green is SDO(MISO)

pink is SDI (MOSI).

Please help to solve this issue.

thanks

Rahul

WT microelectronics

rahul@wtmec.com

9540488549