Other Parts Discussed in Thread: LMK04610, LMX2572, LMK04828, LMX2594, TRF3765, LMX2582

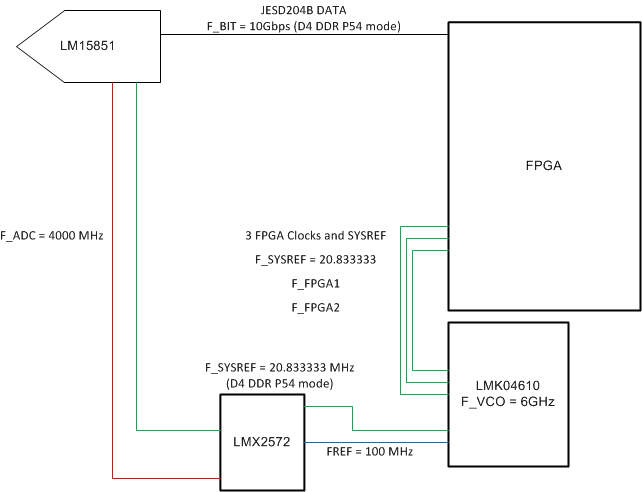

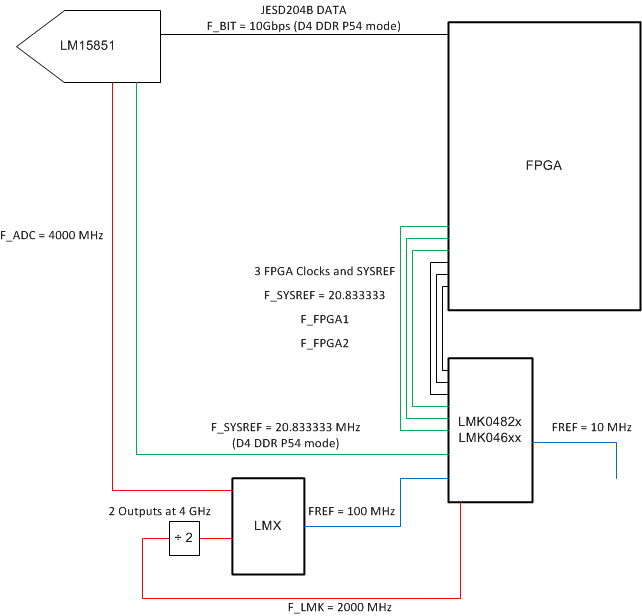

Hi! I need to feed LM15851 with 4GHz device clock + SYSREF and an FPGA with some other device clock + SYSREF (a JESD204B system). As I have seen, there is no suitable clocking solution integrated into a single IC with so high output frequency and JESD204B support. So, it seems that LMK04610 and LMX2572 cascaded somehow would be suitable. Would you be so kind to give some explanation on clocking architecture using these devices? How should the two clocking devices be connected together and with LM15851 and FPGA? What would be SYSREF signal architecture?

Maybe there are more suitable devices, but these two were chosen due to their low power consumption. Maybe you can recommend other devices. Thanks in advance.