Other Parts Discussed in Thread: DAC34SH84

Hello

I am working on dac34h84 evm , i have some question ?

1. can i configure the DAC in fifo disabled mode ? if yes , then what will be reading frequency , reading frequency is depend upon what ?

2. can i give same frequency for data_clk and dac_clk , in fifo disable mode?

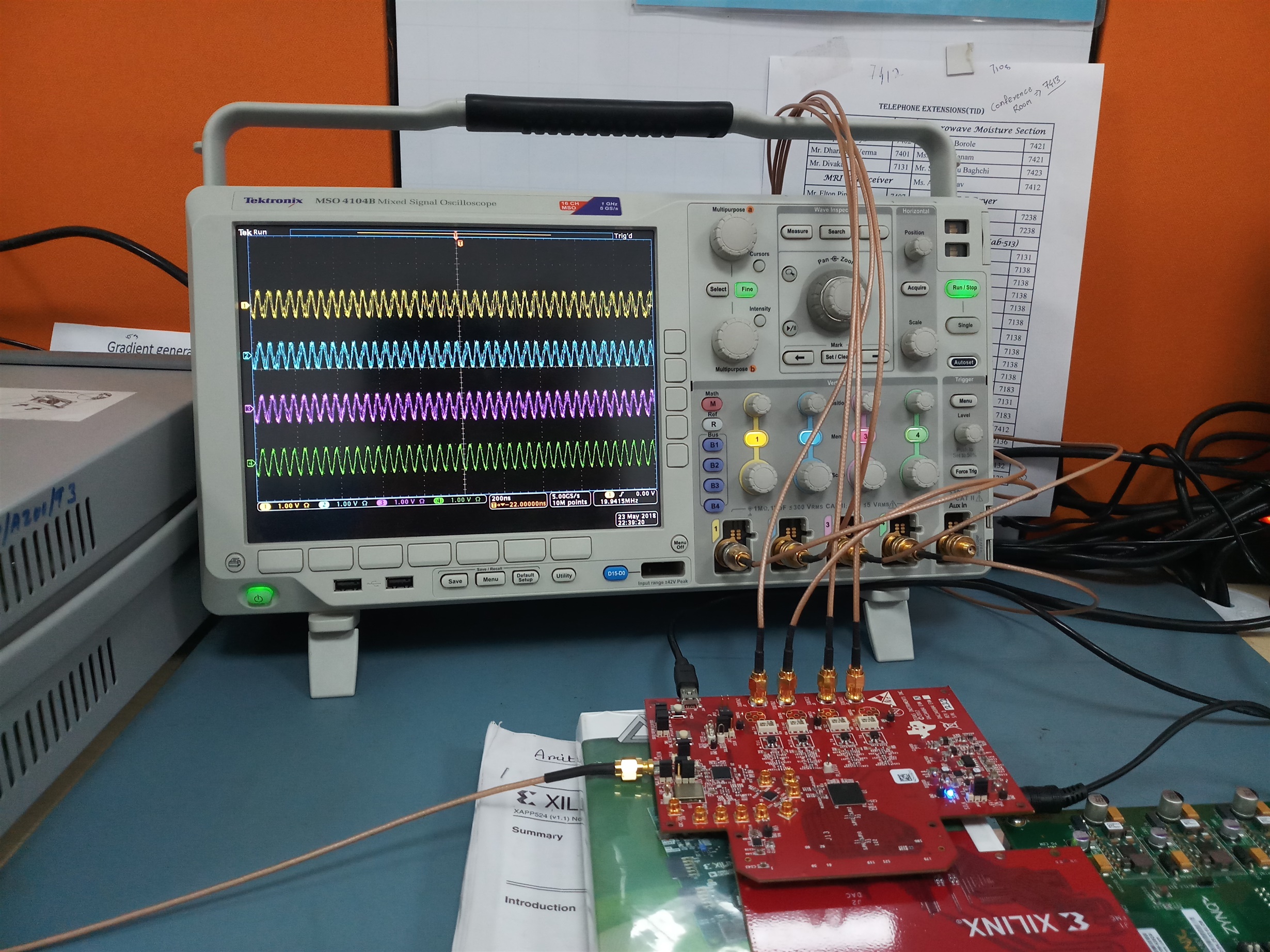

3. On dac34h84 evm "SH3" provides dacclk2 , can i provide this clk to the fpga or get it from fpga as i have fmc dac adapter ? as shown in the images below

4. If i generate the same pattern of wave as shown on the data sheet of dac34h84 page no 26, what are the extra signals which i need to take care like OSTR as i am not using fifo ?