Tool/software: TI C/C++ Compiler

Hello ,

I choose different channel for the ADS8668 by changing the code written into the command register and change the voltage supply for the input.

The data of MISO is always the same. and it's a invalid data.

My code is attached below:

#include <msp430.h>

unsigned long ads8668_reg_read(void);

void ads8668_reg_write(void);

void Init_GPIO();

int main(void)

{ WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

P1SEL0 |= BIT5 | BIT6 | BIT7; // set 3-SPI pin as second function

P2DIR |= BIT1; // CS Port

UCA0CTLW0 |= UCSWRST; // **Put state machine in reset**

UCA0CTLW0 |= UCMST|UCSYNC|UCMSB|UCCKPH;// Clock polarity high, MSB

UCA0CTLW0 |= UCSSEL__ACLK; // Select ACLK

UCA0BR0 = 0x02; // BRCLK = ACLK/2

UCA0BR1 = 0;

UCA0MCTLW = 0; // No modulation

UCA0CTLW0 &= ~UCSWRST; // **Initialize USCI state machine**

PM5CTL0 &= ~LOCKLPM5; // Disable the GPIO power-on default high-impedance mode

P2OUT |= BIT1;

ads8668_reg_write();

while(1)

{

ads8668_reg_read();

}

}

unsigned long ads8668_reg_read(void)

{

unsigned char SPI_RX_BUF[2];

unsigned long retVal;

retVal = 0;

P2OUT &= ~BIT1;

while((UCA0STATW&UCBUSY));

UCA0TXBUF = 0x00;

while((UCA0STATW&UCBUSY));

UCA0TXBUF = 0x00;

while((UCA0STATW&UCBUSY));

SPI_RX_BUF[0] = UCA0RXBUF;

UCA0TXBUF = 0x00;

while((UCA0STATW&UCBUSY));

SPI_RX_BUF[1] = UCA0RXBUF;

UCA0TXBUF = 0x00;

P2OUT |= BIT1;

retVal = SPI_RX_BUF[0];

retVal = (retVal << 8) | SPI_RX_BUF[1];

return retVal;

}

void ads8668_reg_write(void)

{

P2OUT &= ~BIT1;

while((UCA0STATW&UCBUSY));

UCA0TXBUF = 0xC0;

while((UCA0STATW&UCBUSY));

UCA0TXBUF = 0x00;

while((UCA0STATW&UCBUSY));

UCA0TXBUF=0x00;

while((UCA0STATW&UCBUSY));

UCA0TXBUF=0x00;

__delay_cycles(600);

P2OUT |= BIT1;

}

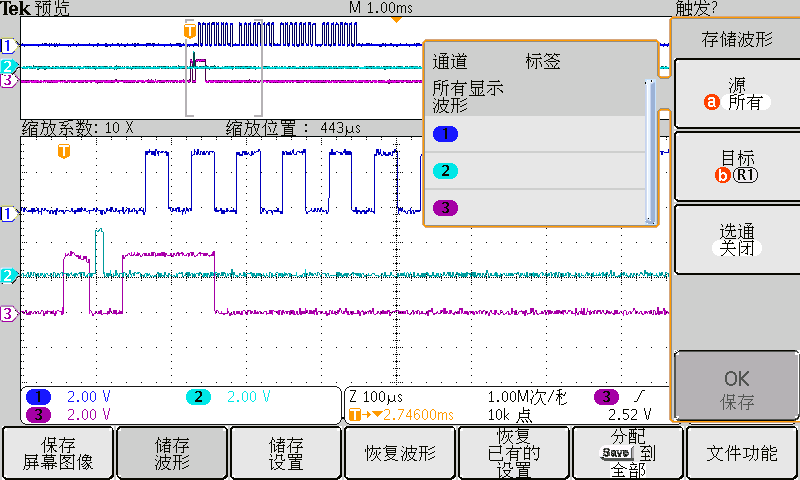

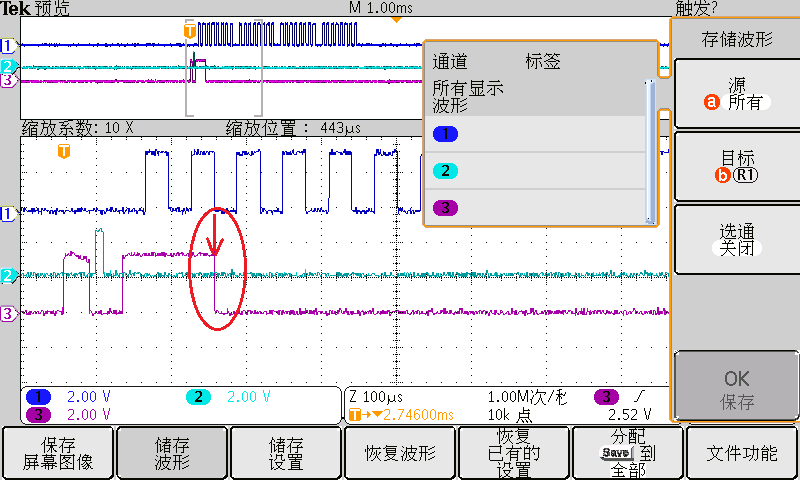

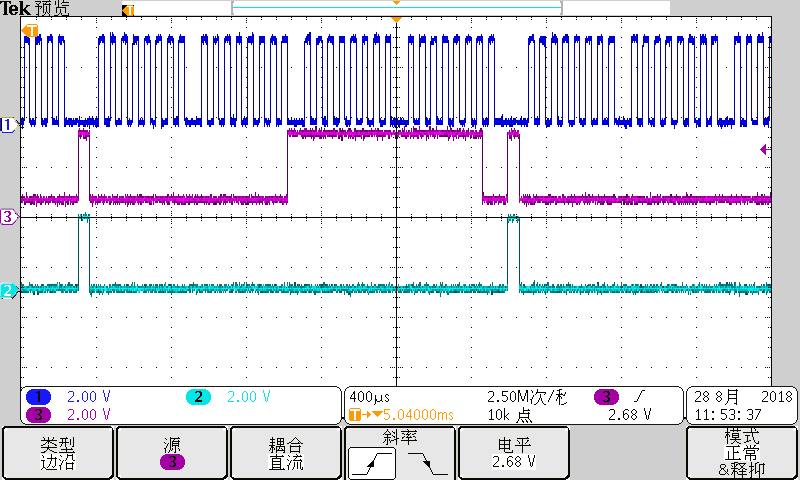

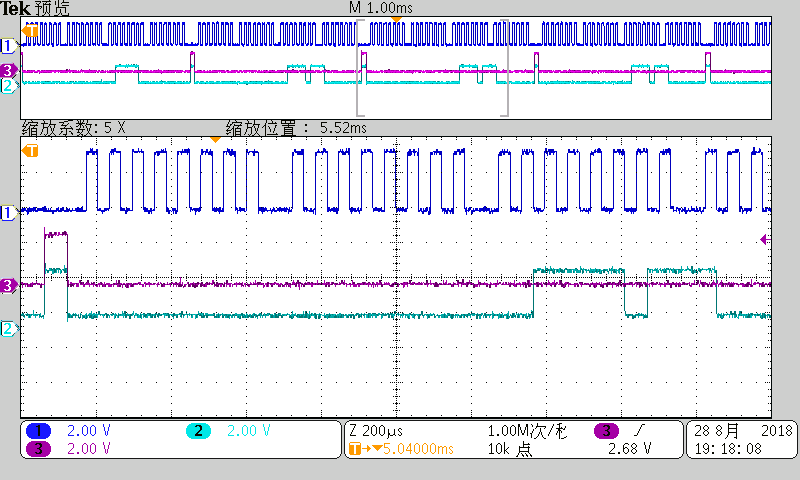

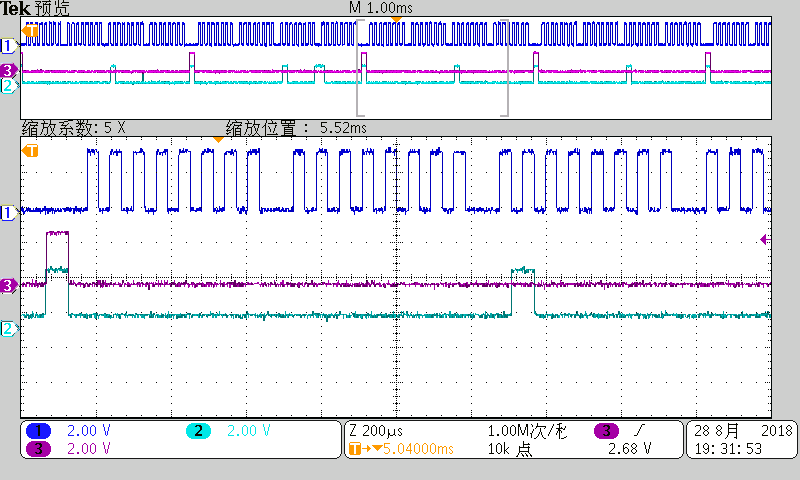

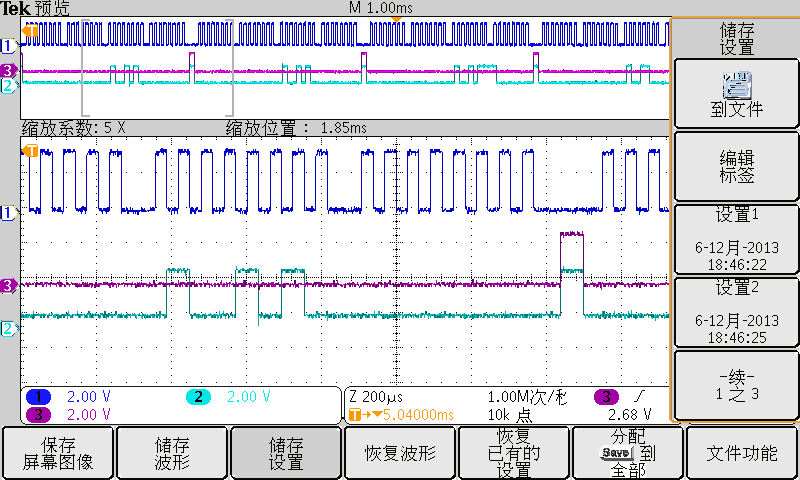

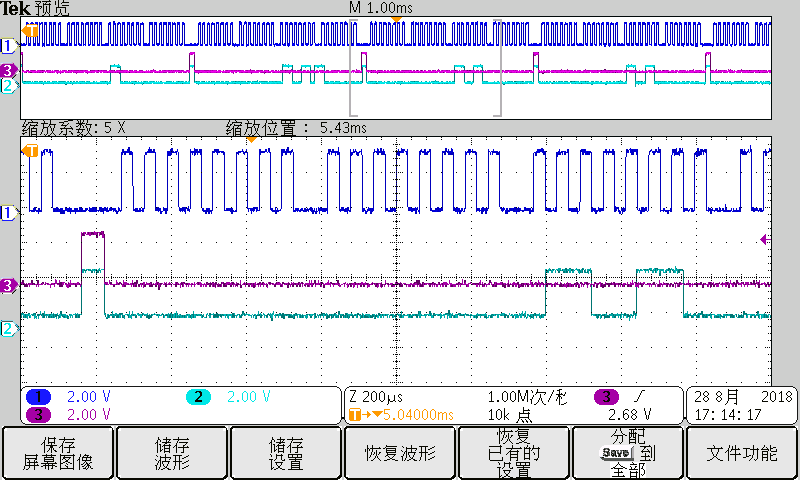

And the plot of first 32 SCLK's CS; MOSI; CLK acquired by oscilloscope is as below:

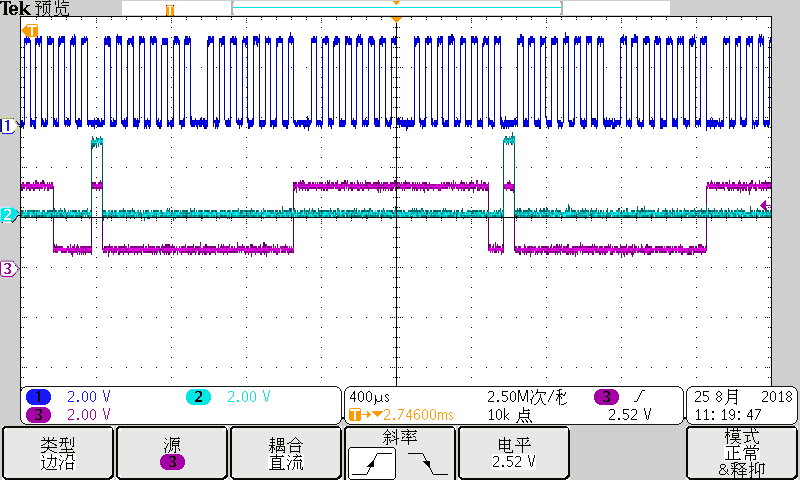

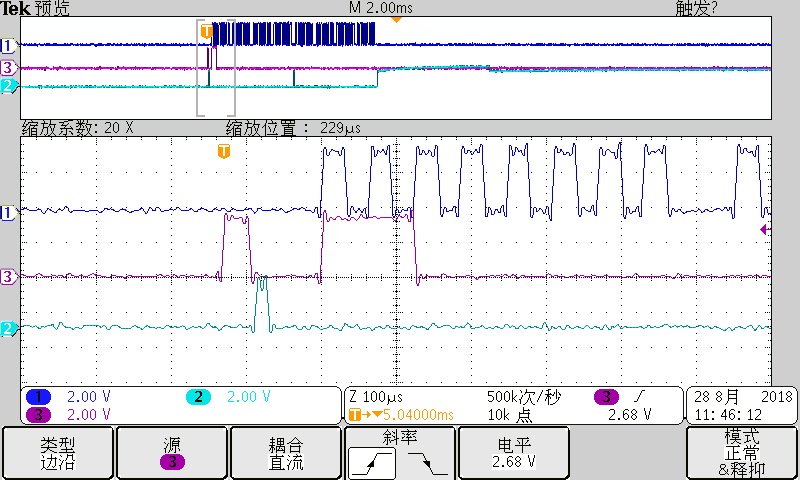

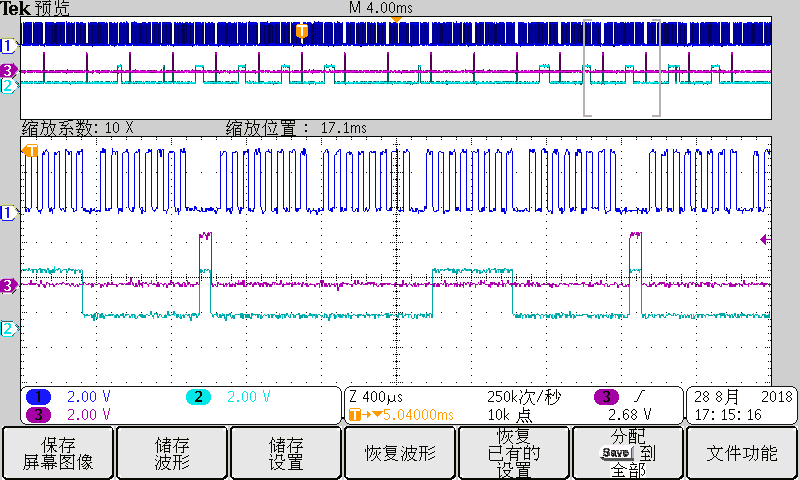

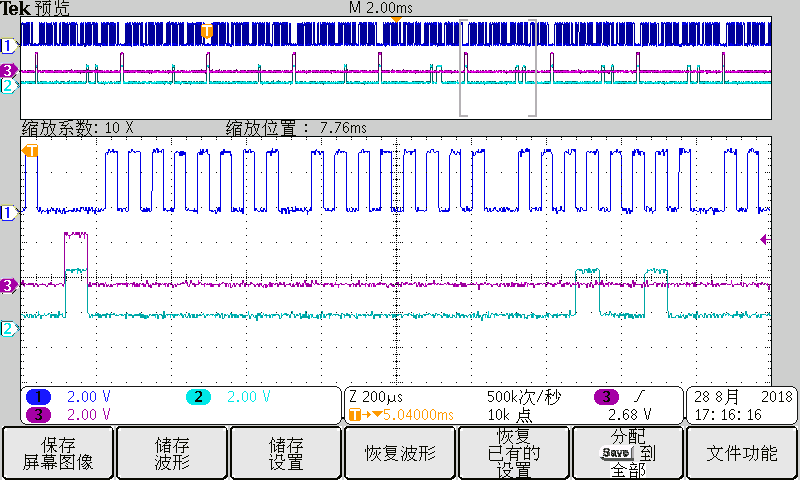

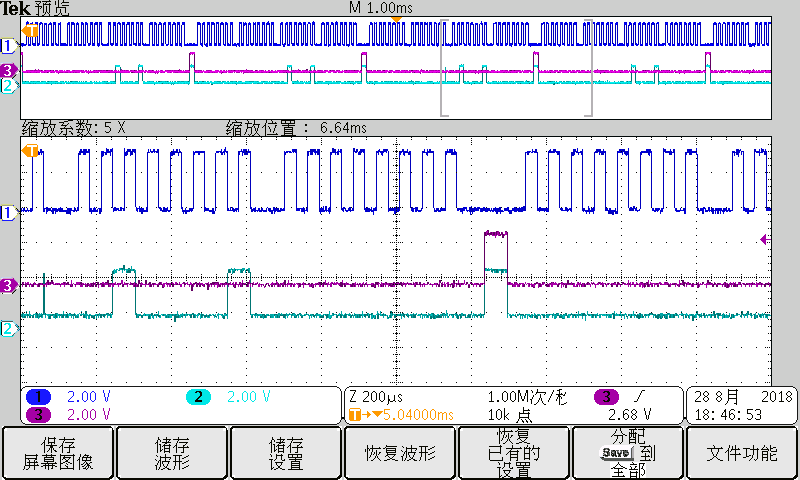

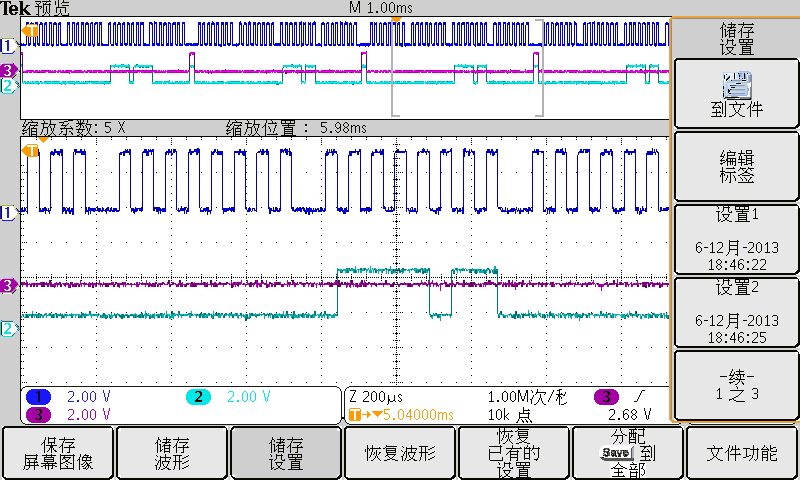

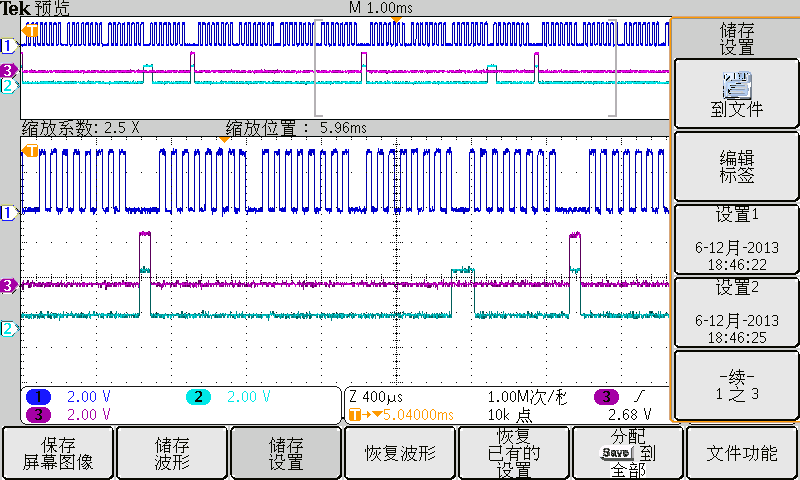

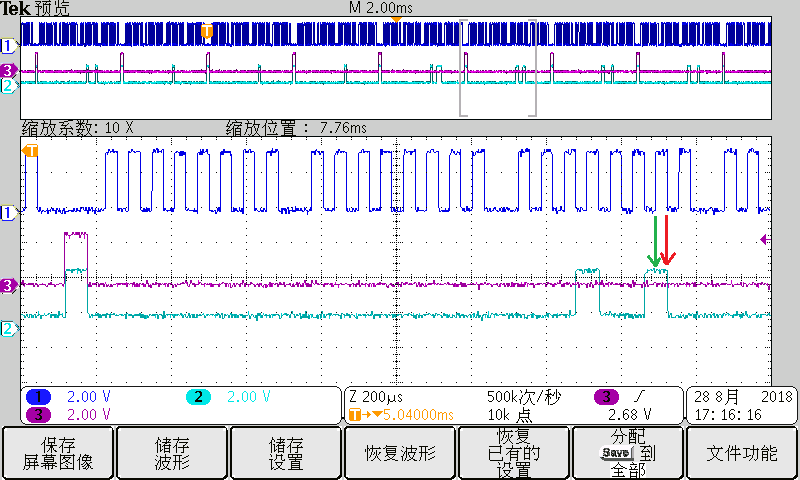

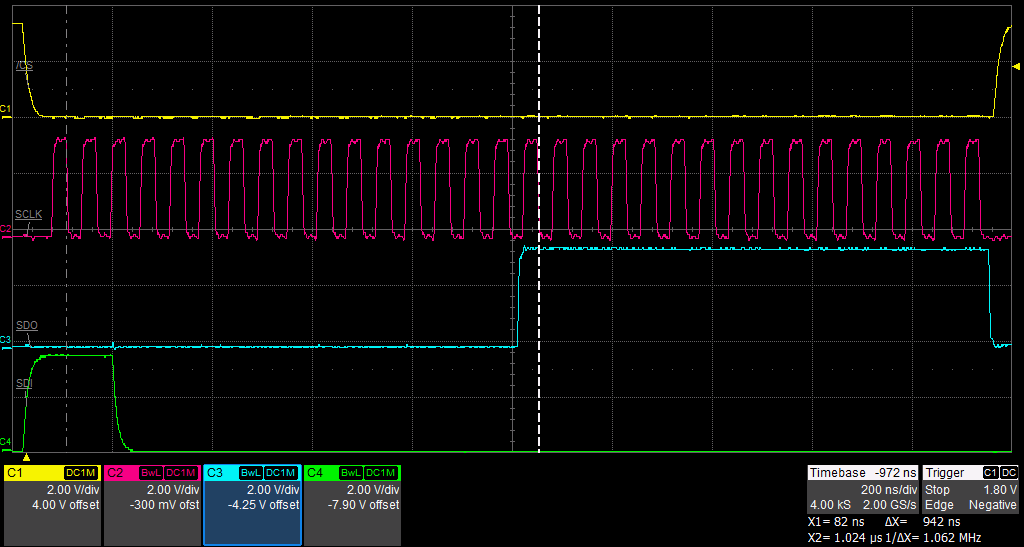

And the plot of MISO;CS;CLK is as below:

The MISO is the purple line and it won't change no matter what I do to the input. So I'm here to ask for help.

Thanks.