Hello,

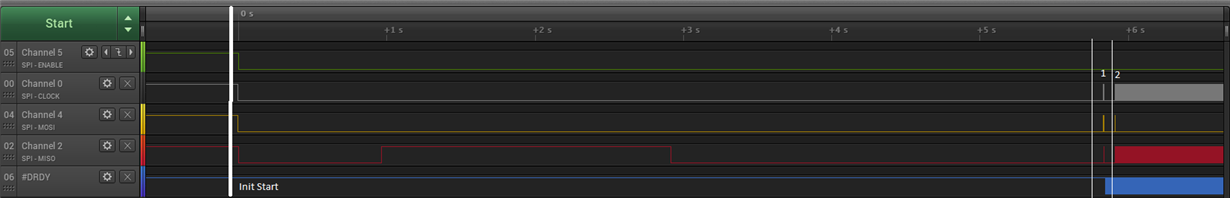

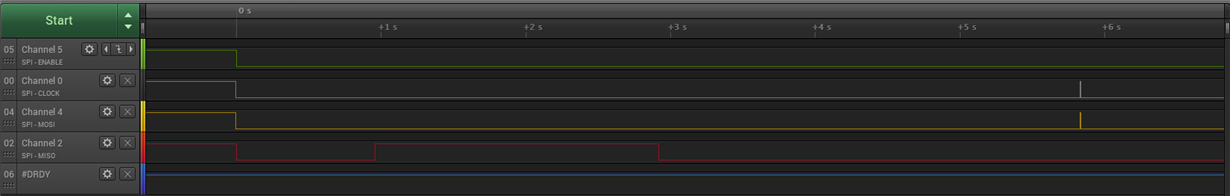

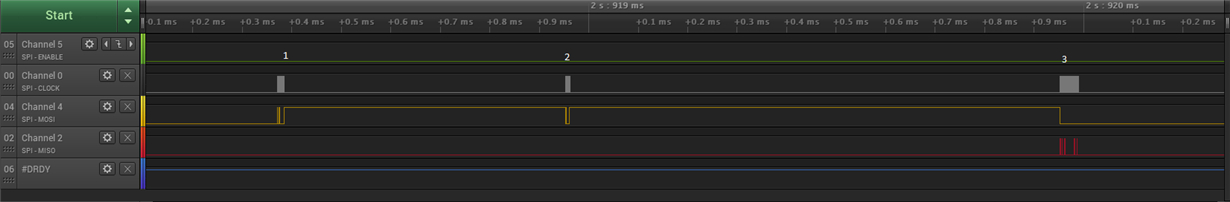

I am using two ADS127L01 in daisy-chained mode with a microcontroller (STM32F7) and experiencing strange problems regarding the data I receive via the SPI bus. The MCLK is delivered via the microcontroller.

The procedure I am using is as follows:

1. Setting START pin and #CS pin low

2. Setting the master clock to 720kHz

3. Initializing the SPI to 1.6875MHz

4. Setting the #RESET/#PWRDN pin low and waiting ~3000ms

5. Setting the #RESET/#PWRDN pin high and waiting ~3000ms

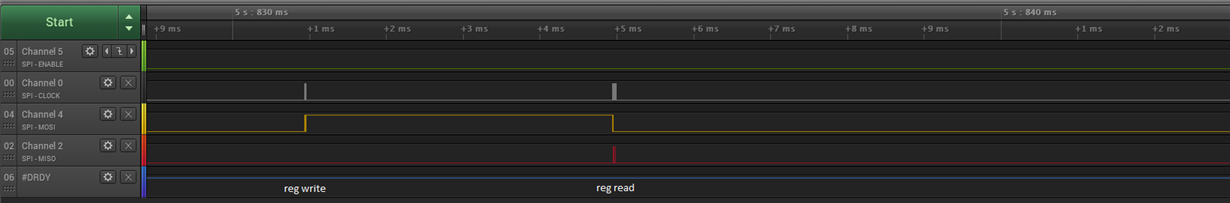

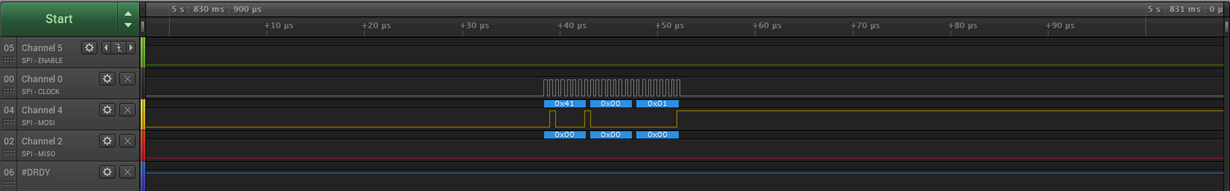

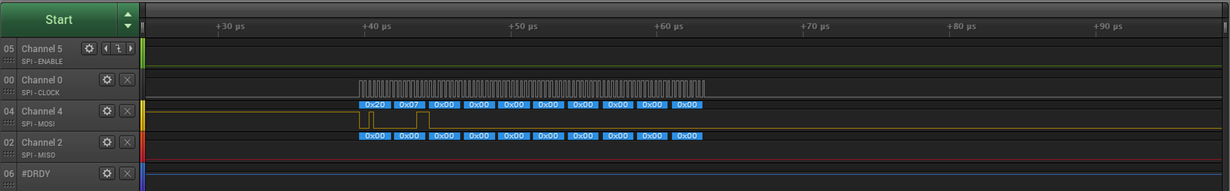

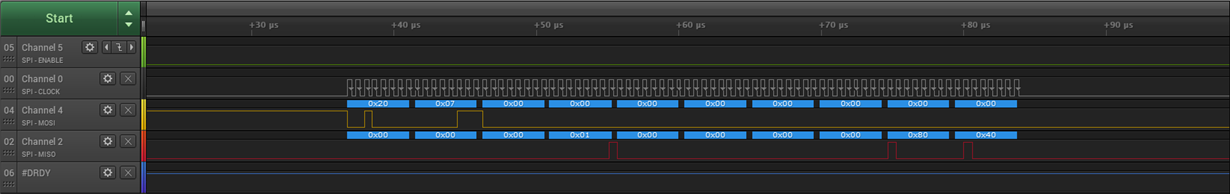

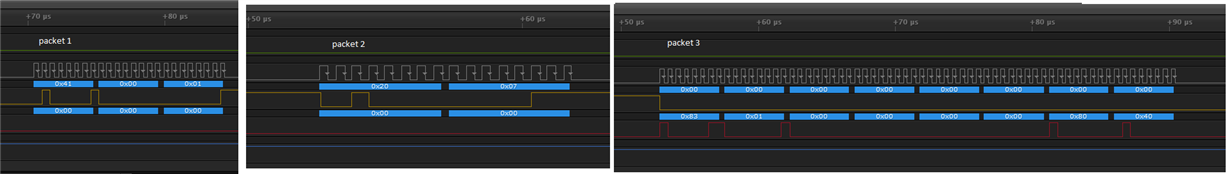

6. Sending {0x41, 0x00, 0b00000001} to the ADC to set up the CRC-8 mode

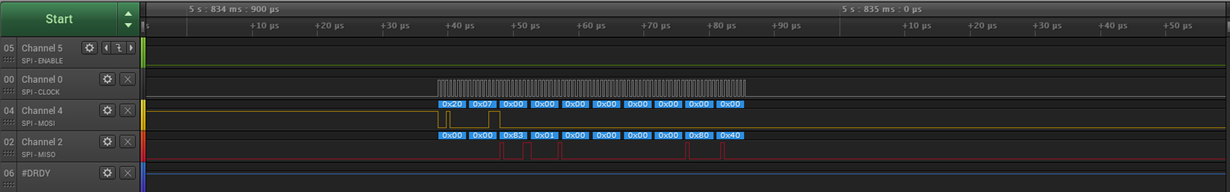

7. Sending {0x20, 0x07, 0, 0, 0, 0, 0, 0, 0, 0} to the ADC to read all registers

Here I get the first errors: I am expecting returned bytes {0x83, 0x01, ..., 0x80, 0x40} from the device registers, but sometimes I get {0x00, 0x01, ..., 0x80, 0x40}. It seems that the first byte gets lost. When I lower the SPI clock the error may disappear. If I put in an extra delay between the operations it seems also to work. It looks like the first SPI clock edge has to come at the right time. Because I have to read 8 bytes (4 bytes from each device), the SPI clock has to be higher than 22.5kHz * 64 = 1.44MHz.

Let's assume the error does not appear, the procedure continues:

8. Setting START pin high

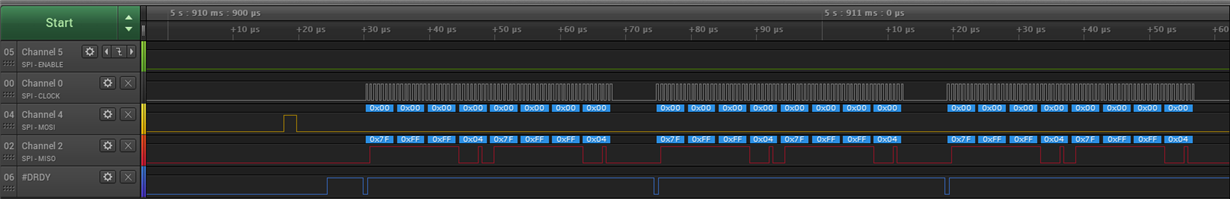

9. Start gathering data in "continues mode":

9.1 Waiting till #DRDY goes low

9.2 SPI clock rises high after ~375ns, #DRDY goes high

9.3 SPI reads 8 Bytes

9.4 After the last SPI clock cycle goes low, there are ~6.5us till #DRDY goes low

9.5 Restart from step 9.1

Here another error appears sometimes: Like in Point 7 explained, the first byte can get lost. When the error not occur, the CRC value looks fine. Because I am using the ADC's for IEPE-Sensors I can not say at the moment if the data values are valid. I will get to this part later.

For now I am interested in the correlation of the MCLK and the SCLK. But I can not find anything about that in the datasheet. Can you explain this correlation to me?

It seems like the MCLK has to be at least 0.5 * SCLK. This would mean, that with more than 2 devices I can not reach the maximum data rate in daisy-chained mode. In the datasheet, the equation 11 states that the total number of devices depends only on the SCLK.

Thanks for your help!

Greetings,

Reggie

EDIT: Sorry, I forgot to mention that all SPI read / write values are confirmed with a logic analyzer.