Other Parts Discussed in Thread: ADS8339

Hello,

I'm using a TLV2553 multi channel ADC. The output pins (data out and EOC) are connected to an analog devices level shifter P/N: ADG3304

For some reason the output pins will not drop all the way down to zero.

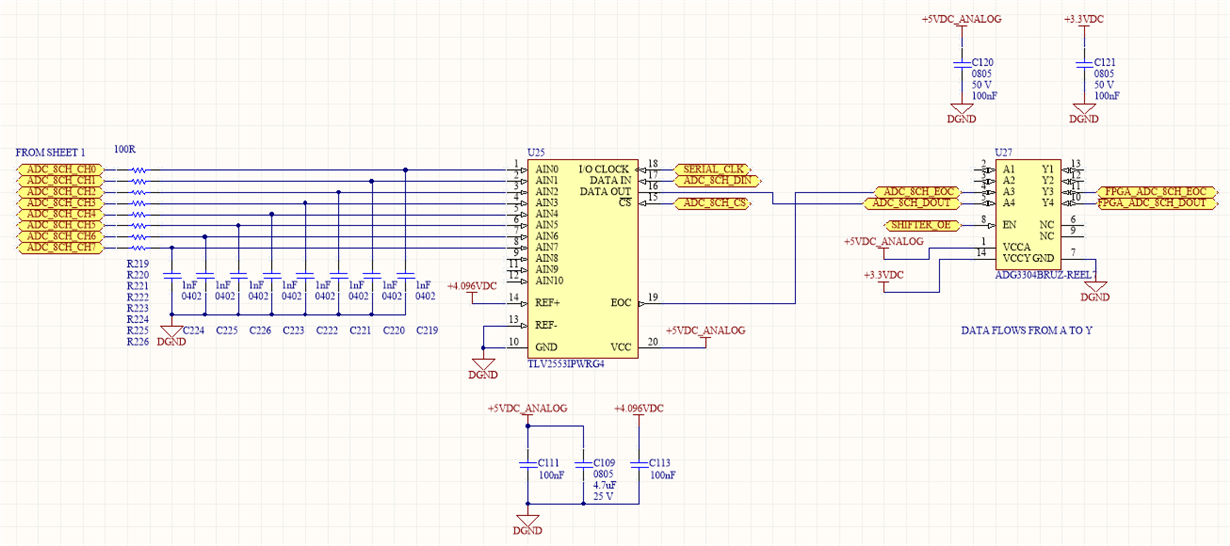

Here is the schematic:

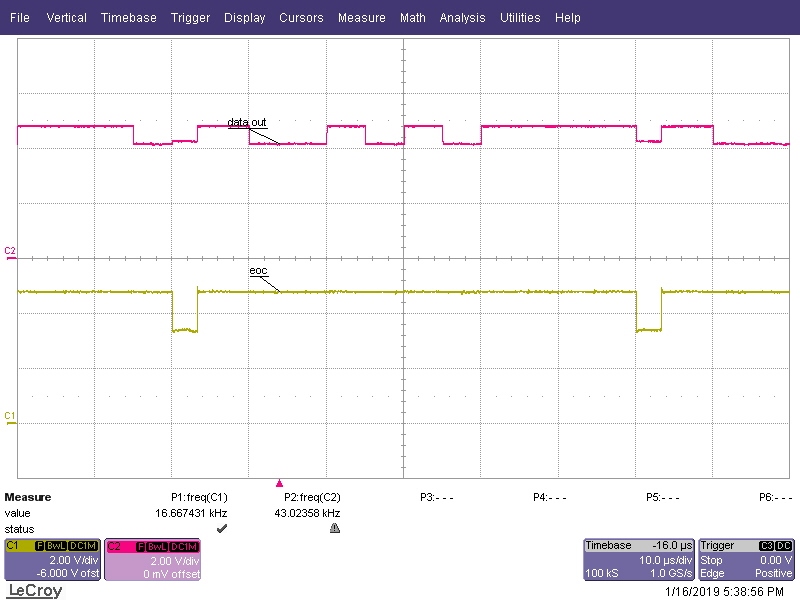

And here is the waveform of the output pins. "data out" is measured at u25 pin 16. "eoc" is measured at U25 pin 19.

Why will these signals not drop down to zero volts in the off times?

Note that I have also connected the output pins of another part, ADS8339, to the same level shifter (separate part) and the output pins drop to zero just fine.

Thanks in advance