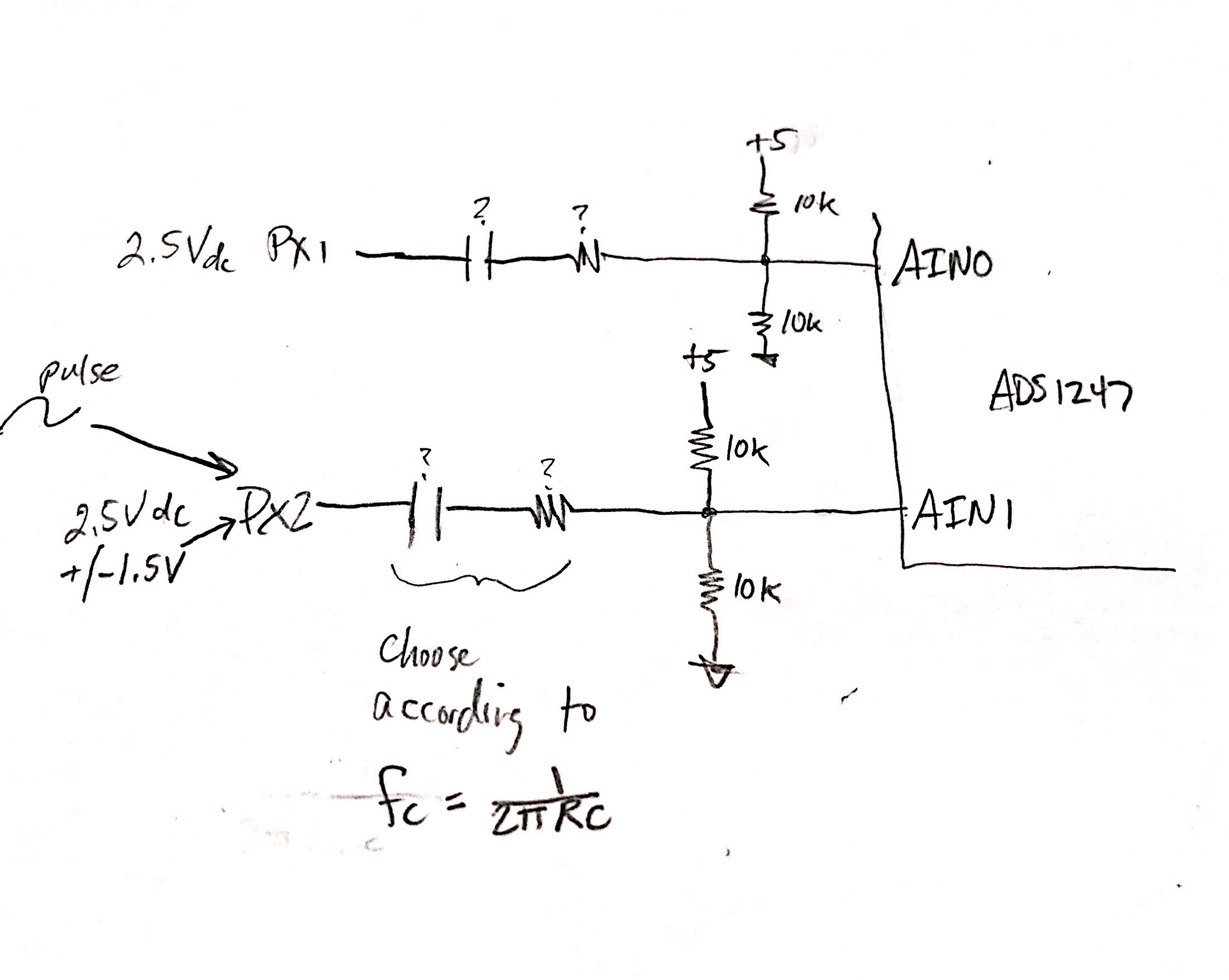

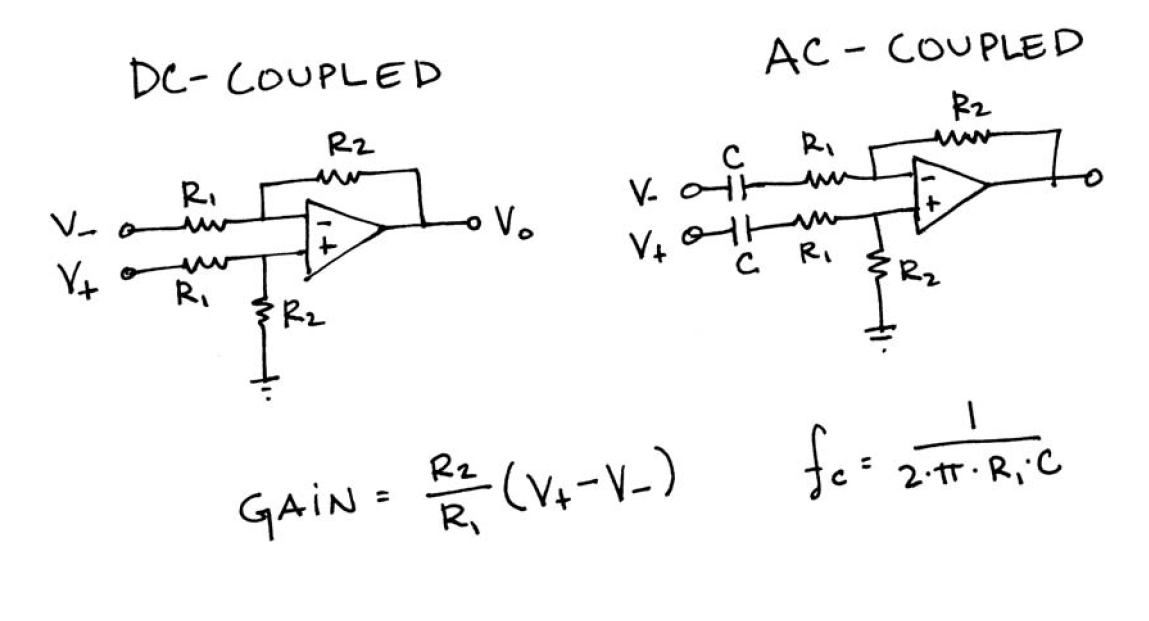

I have an application where I want to measure pulses, and the DC component is unimportant. I do not need to measure these pulses accurately as far as magnitude. Has anyone successfully put series capacitors feeding the ADC in a capacitively coupled architecture? What size caps did you use?

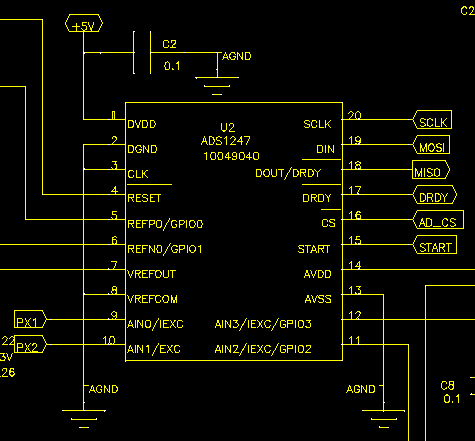

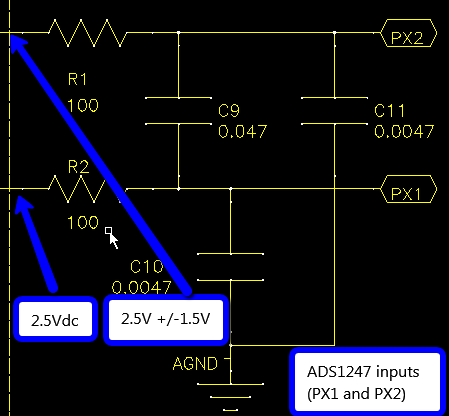

In my existing configuration I am measuring between a 2.5V reference and a signal that swings 2.5V +/-1.5V. I use PGA = 1. I have an XtoY filter on the front end, as well as low value series resistors.