Dears.

I need help with the problem of the AFE5808A.

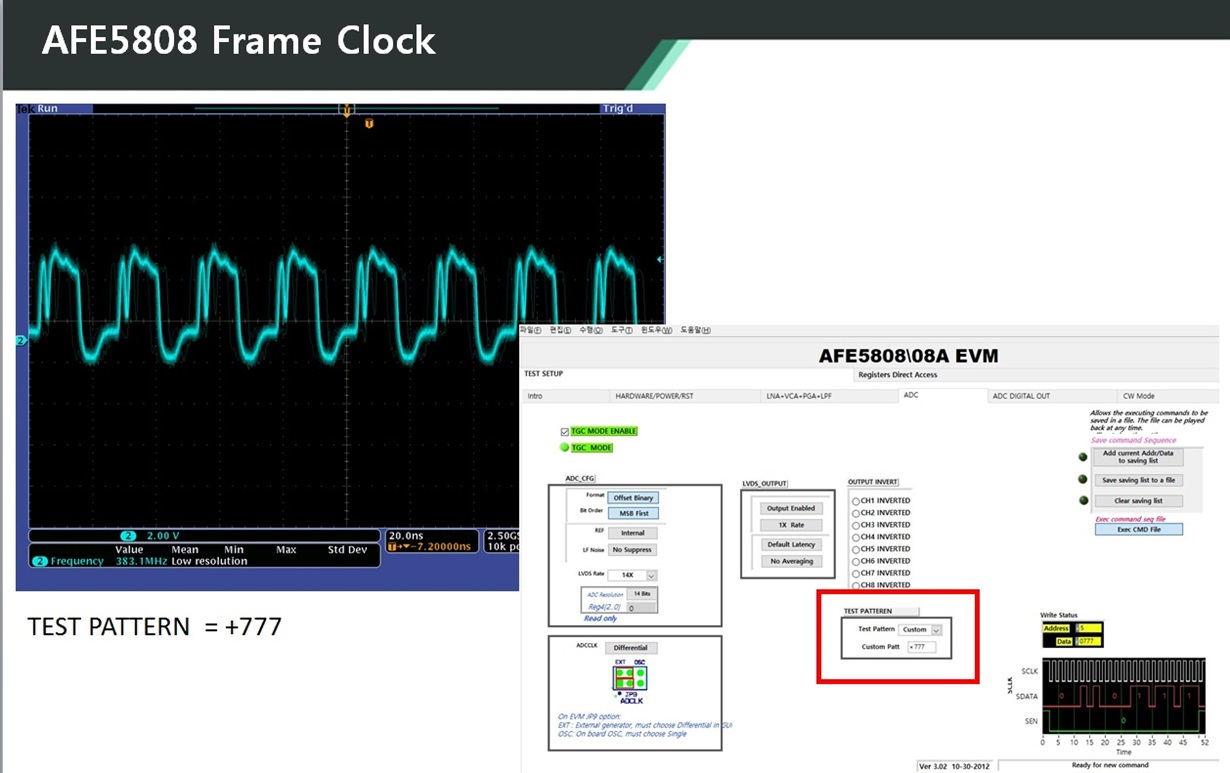

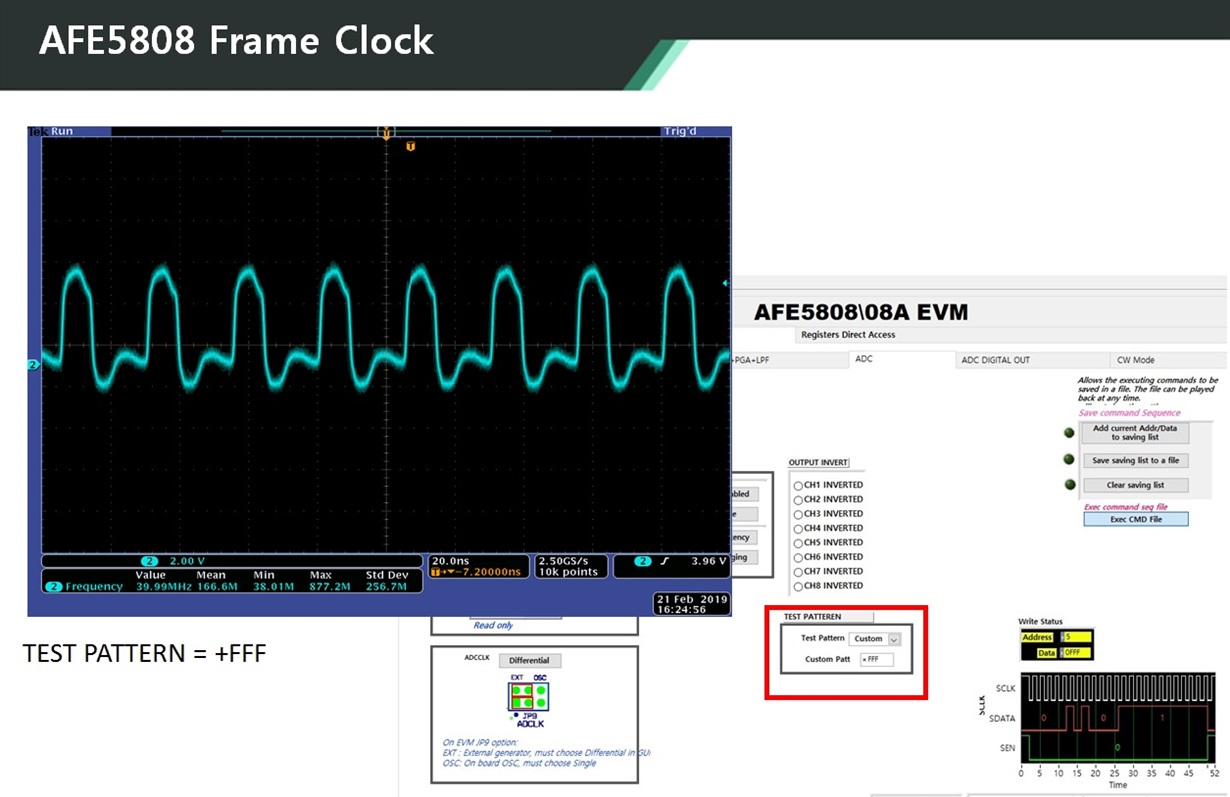

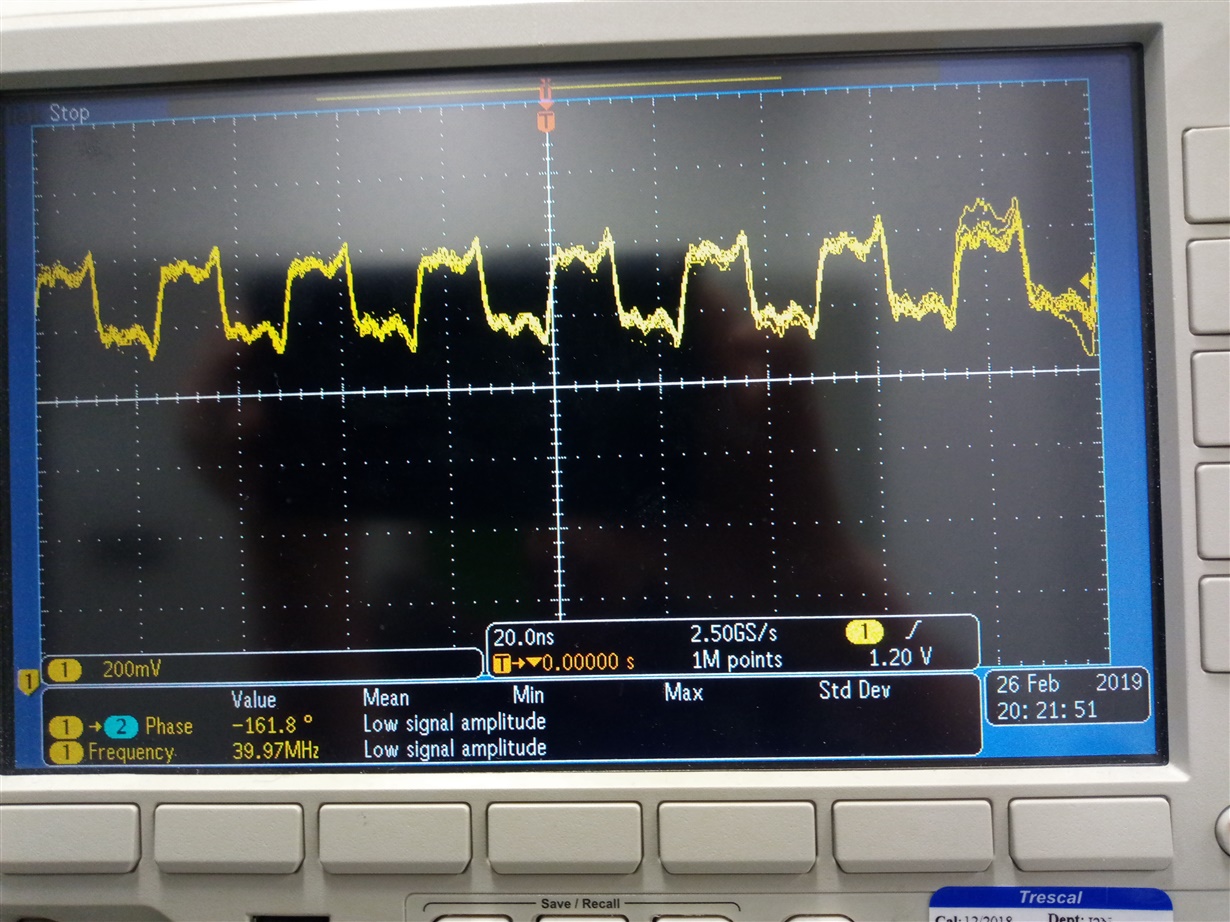

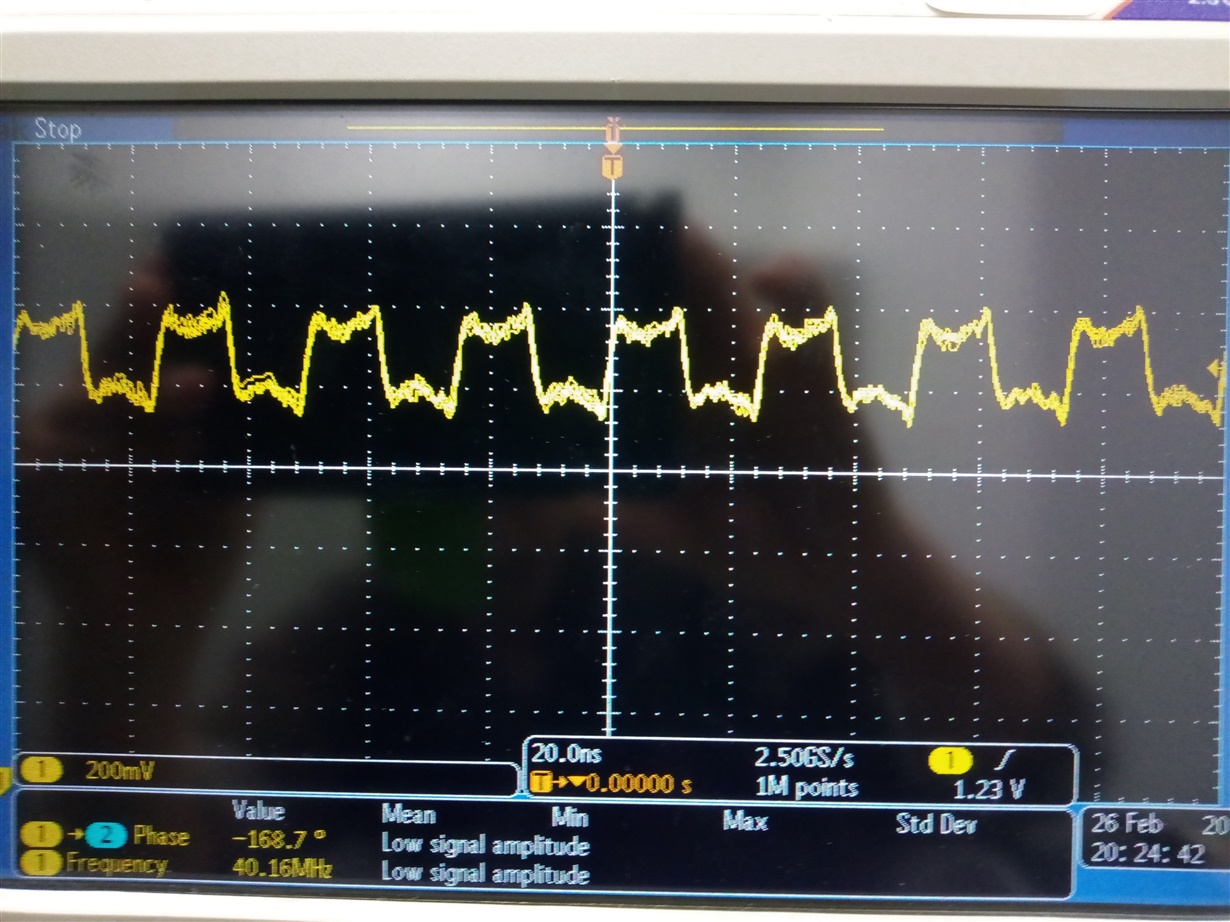

When Frame_CLK of AFE5808A is inputted to FPGA (Cyclon 4), inputting "TEST PATTEREN" custom data in UI of AFE5808A changes Frame_CLK of AFE580A.

Does Frame_CLK change depending on the value of the custom data input?

Thank you.