Hi Chris,

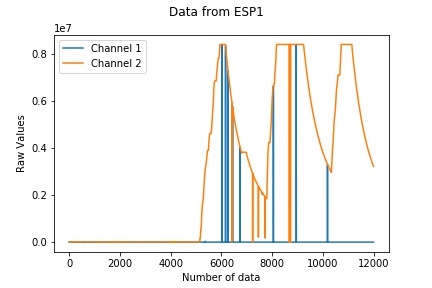

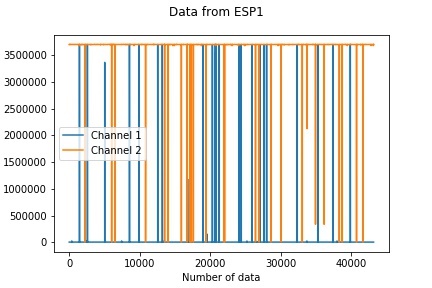

I am collecting data of 2 ADC channels on the ADS1256. The below are the images of the two separate trials

The first channel I connect it to ground, the second channel I connect it to a PSU and I change its output voltage. As you can see, the noise is coupled between the two channels. The plot shows that the noise amplitude of the first channel (GND) is capped by the profile of the second channel (PSU voltage).

I wonder what might be the cause of this problem.

Thanks,

Khoi Ly