Other Parts Discussed in Thread: TINA-TI, , LMX2594

Tool/software: TINA-TI or Spice Models

Hi,

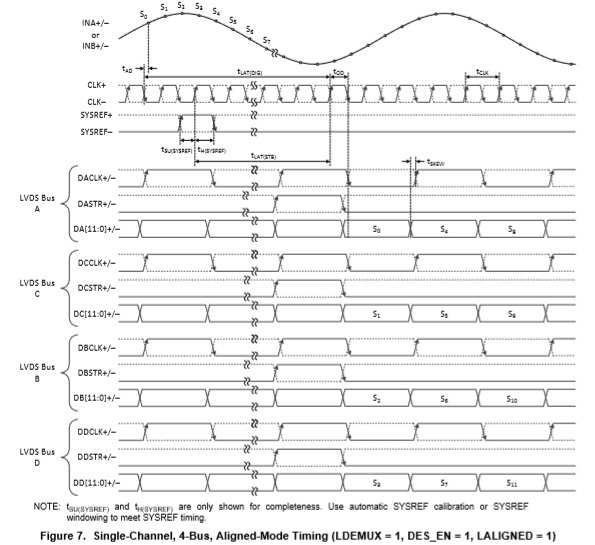

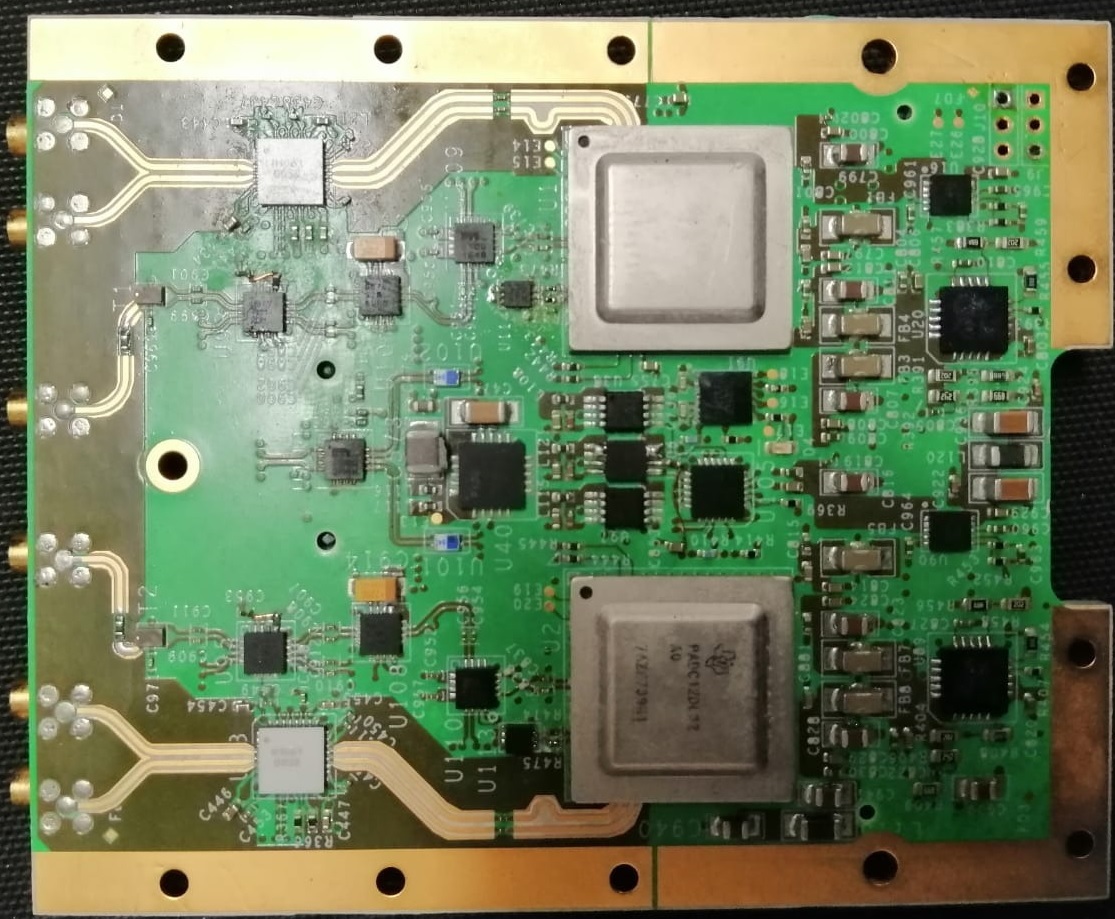

I'm design a board with four ADC12DL3200 and now I'm trying to sync the ADCs.

I've enabled the SYSREF receiving setting

- SYSREF_RECV_EN = 1

- SYSREF_PROC_EN = 1

- SYSREF_LVPECL_EN = 1.

I've send SYSREF signals to the ADCs and I've verified that the bits

ALIGNED =1

REALIGNED = 1.

Then I've measured the data phase match and change the phase of a specific SYSREF signal.

I've resetted the ALIGNED and REALINGNED bits and send several SYSREF signals.

After this I've verified that the ALIGNED = 1 but REALIGNED = 0!

Why the SYSREF signals are received but not processed?

Is there a specific comand to able the processing?

i'm looking forward to hearing from you

Regards.

Daniele Sassaroli