Other Parts Discussed in Thread: AM5728,

I wanted to try programming registers on this part. I'm using a PRU core on an AM5728 to generate the SPI signals. However, I am not sure that I am doing this correctly.

I wanted to set register 5 (OUTPUT_DATA_WORD_CFG) to a value of 0x02 (enable fixed pattern in the output data word) and then read it back from the device.

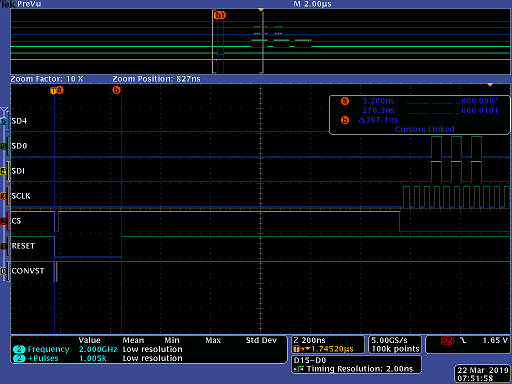

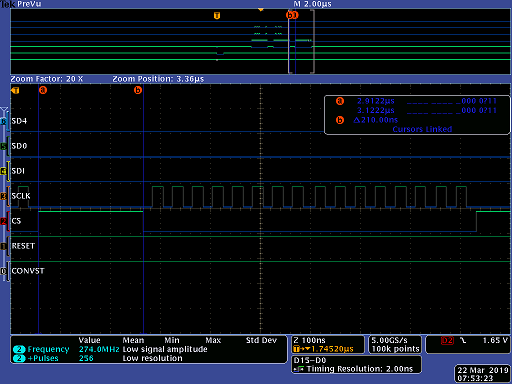

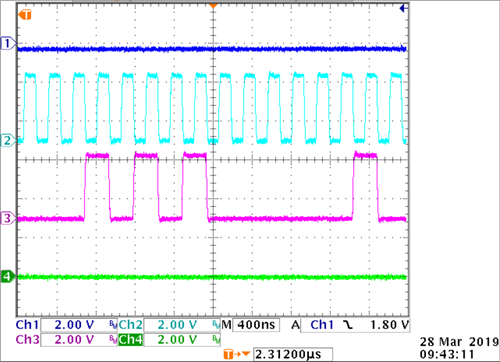

Here is how I reset the device (267ns low gong RESET pulse, CS and CONVST high incidentally):

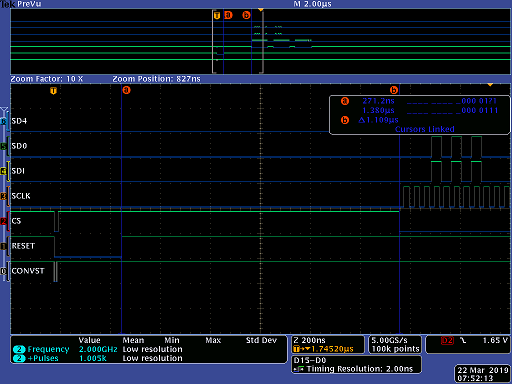

Then, I wait 1.1us before issuing and SPI communication:

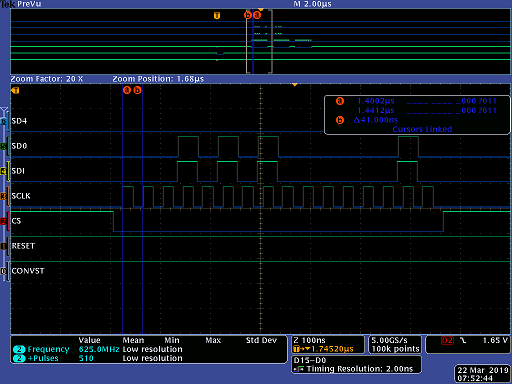

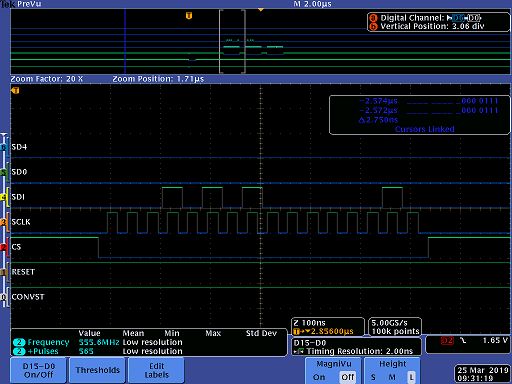

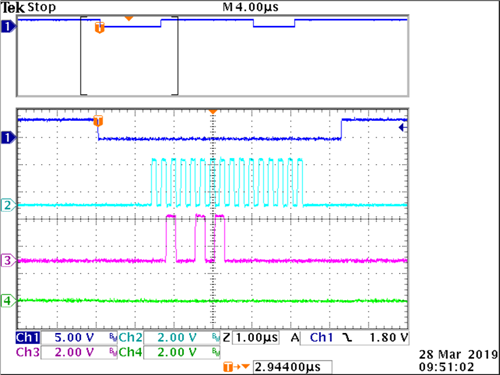

Then, I write to register 5 (send 0x1502 let me know if this looks ok). Notice how SD0 mirrors what I put into SDI.

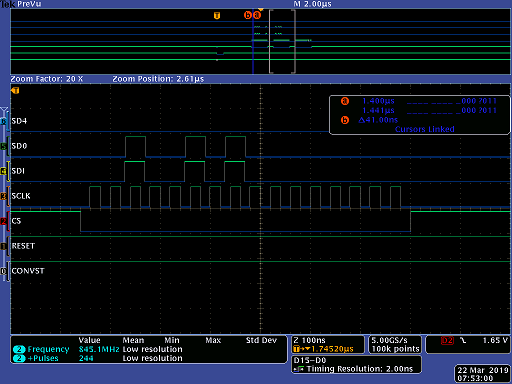

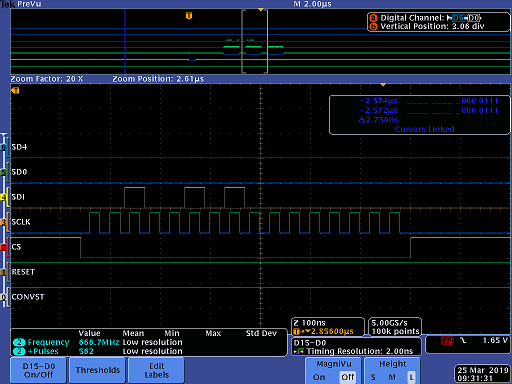

Then, I send command to read from register 5 (send 0x2500 let me know if this looks ok):

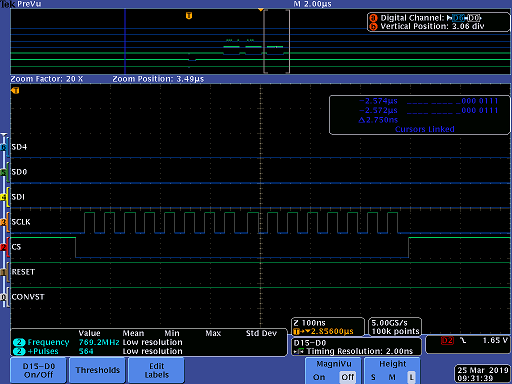

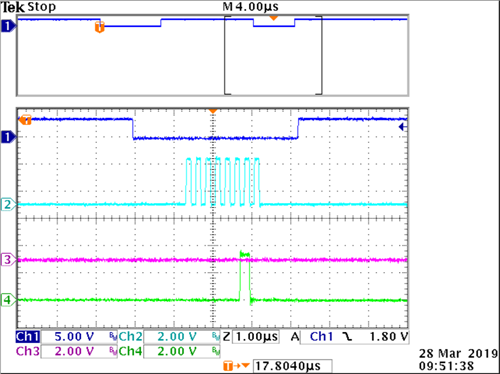

The datasheet says that the read results are returned in the next frame, so I send in (0x0000), expecting to see something returned on SD0 but 0 is seen on SD0.

Am I doing this wrong?