Hello!

I'm trying to understand how to configure the DAC38J84 mounted on TSW3XJ8XEVM to produce 1228.2 MSPS on four channels, so essentially the maximum possible data rate specification.

Using the TSW3XJ8XEVM GUI I select

DAC Input Data rate = 1228.2

Interpolation = 1

Number of SERDES Lines = 8

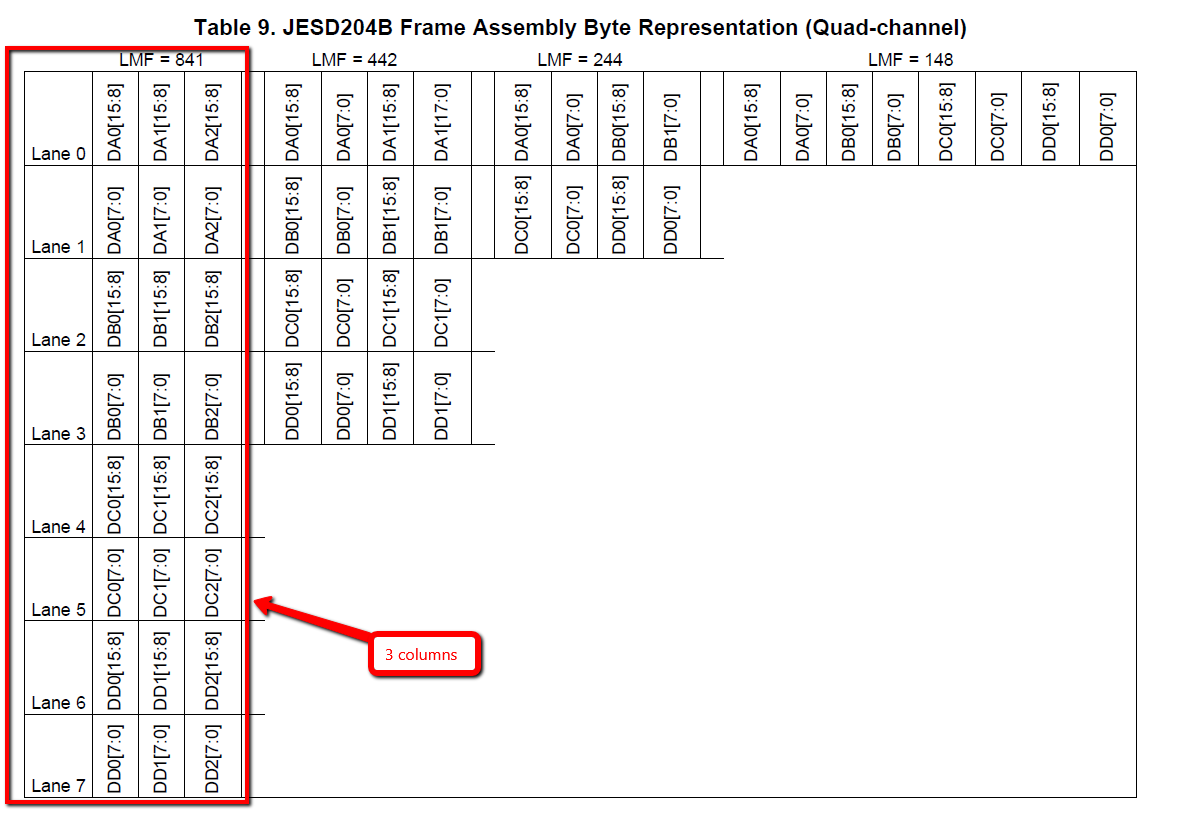

I assume that the DAC38J84 manual (Table 9) configuration LMF = 841 is the one I'm using (confirmed in the DAC JESD block tab in the GUI). What confuses me is the illustration of the transfer over the JESD204 lanes which is illustrated in table 9 of the DAC38j84 manual.

My assumption is that in one frame:

Lane 0 the most significant 8 bits of the sample0..2 for converter A are transferred.

Lane 1 the least significant 8 bits of the sample0..2 for converter A are transferred.

Next I'm assuming that one frame lasts 4 FPGA clock cycles. I would expect that in 1 FPGA clock cycles at (307.2 MHz) 4 samples per converter to be transferred, but the table only illustrates 3 samples per converter. Therefore I'm having trouble understanding how the data rate is achieved.

Best regards

Blaz Kelbl