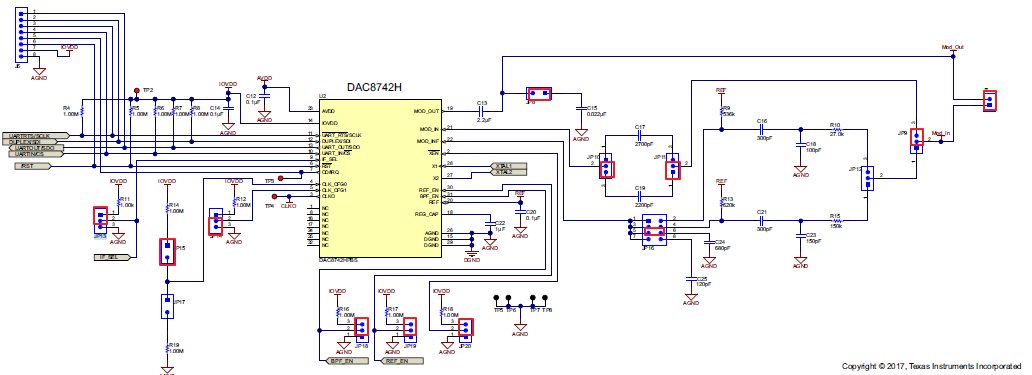

Other Parts Discussed in Thread: DAC8742H, ADS8166, DAC8741H

Hello,

I configurate modem setting

REEST : 0x07 0x00 0x01

MODEM_STATUS Register : 0x20 0xdc 0x24

CONTROL Register : 0x02 0x80 0x4c

MODEM_IRQ_MASK Register : 0x21 0x7f 0x3f

MODEM_CONTROL Register : 0x22 0x00 0x4d

FIFO_LEVEL_SET Register : 0x25 0x00 0xff

PAFF_JABBER Register : 0x27 0x00 0x02

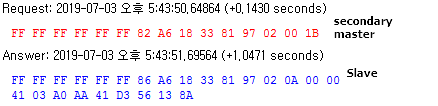

I send data 0x23 0x00 0x11 for transmit data and send data 0xa4 0xff 0xff 0xff 0xff 0xff for receive data.

So I receive right data 0xa4 0x01 0x11.

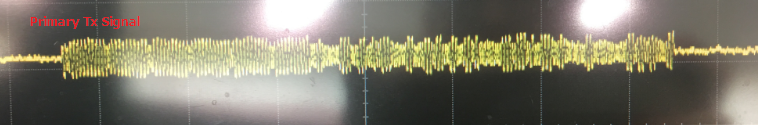

I want to make hart frame and must send much of data at the same time.

I send first data 0x23 0x00 0x11, and send second data 0x23 0x00 0x77.

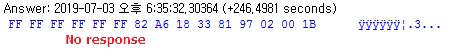

But I just receive first data(0xa4 0x00 0x11). I send data 0xa4 0xff 0xff 0xff 0xff 0xff, 0xff 0xff 0xff for receive data.

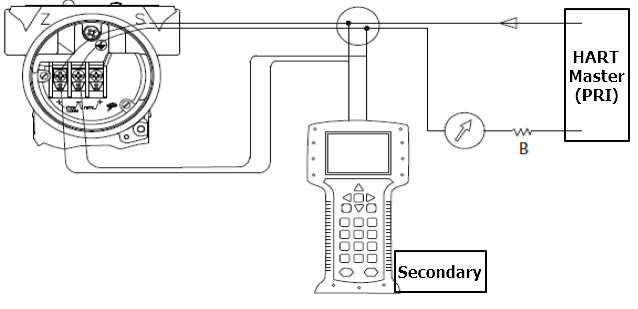

I have been connected MOD_IN and MOD_OUT and it configure ST MCU(master) and DAC8742h(slave).

I do not know if modem settings are wrong or if I sent the wrong data.