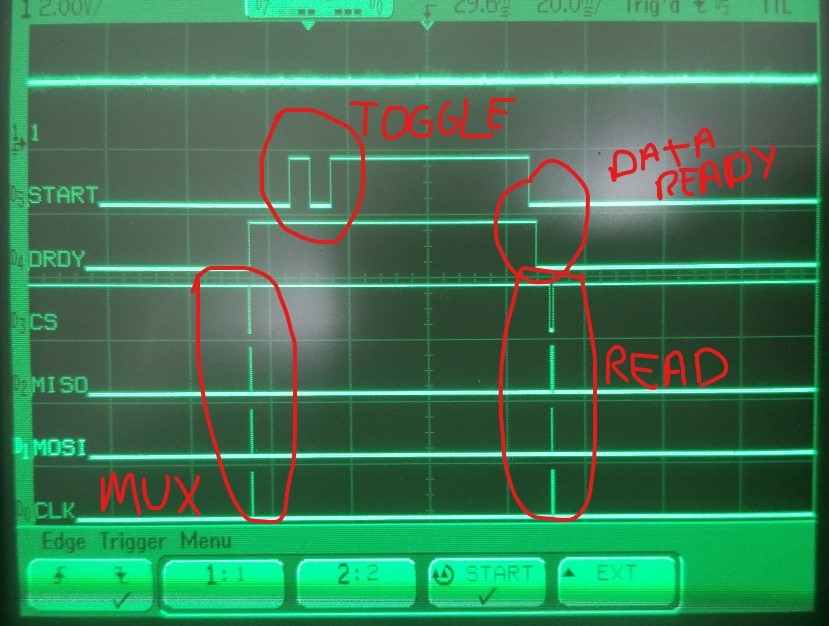

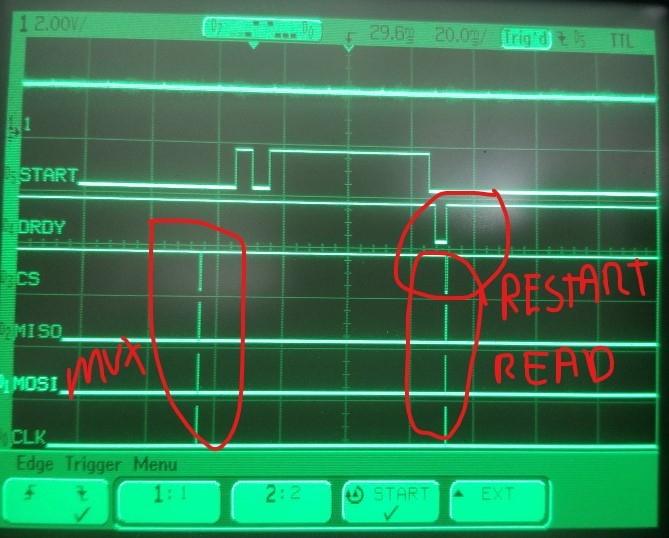

I am experimenting with a very interesting error of communication/acquisition with ADS1263.

Here is the setup:

- Using RPI to access the SPI

- Internal clock

- External reference voltage (2.048) connected AIN0-AIN1 (Single-ended - Neg Grounded)

- Scanning among across all AIN (DIFF) and VDig, Vana, TDAC and TEMP.

- Using serial command to start the acquisition

Everything is working fine, the data is clean, except the ADC1263 starts to reply data corrupted randomly after a few hours, sometimes a day. Interesting though, the same DOESN'T happen if I use the ADS1263 internal reference. It seems the chip reset itself, or at least, the REFMUX switch to the internal reference (reading sometimes is compatible if I am using internal reference - not always).

I have implemented many different traps in my code and looks clean, it is working short term and long term with internal reference. Any clue where should I start to look?

thanks, --fernando