Other Parts Discussed in Thread: DAC3174

Dears:

Could you kindly help to check the schematic and parameters, since we use our DAC3171 to replac ADI's AD9743, there is some issue about our design:

1. DAC3171's Parameters:

Address 0x00 Data 0x46FC

Address 0x02 Data 0x3F80

Address 0x03 Data 0x0001

2. Issues:

Monotonic signals are sent by the FPGA,and the before design using ADI's AD9743. TI and ADI's bit width is 10 bit, both clock and power are the same.

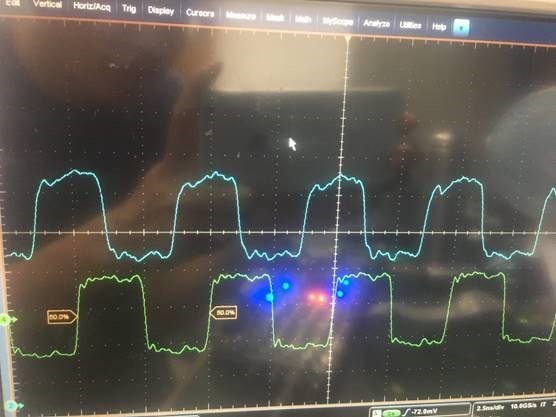

1) The noise base of DAC3171 monotone signal is much higher than that of AD9743 monotone signal.

2) DAC 3171 has a lower noise base and keeps the full range of DAC when it is used in two-tone and four-tone signals.

3. Pls. refer the below schematic and ware forms.

a) Schematic:

b) DAC3171_1tone

Pls. give some advice about our design, we want to replace ADI successfully.

Pls. help us.