Other Parts Discussed in Thread: ADS125H02

Hello E2E forum members,

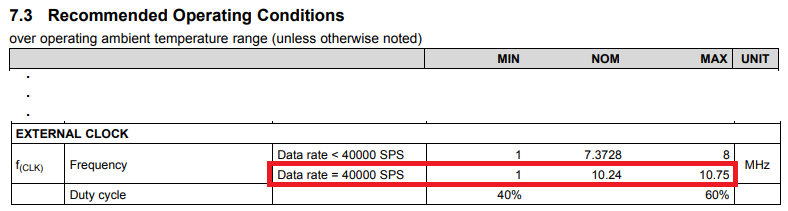

I'm having trouble getting the EVM to do anything that I think it should. It IS producing data. I'm trying to configure it to produce 40,000 sps sinc 5 filtered data. It is running on its internal clock. So that is 7.378 MHz +/- a couple percent Not 10.24MHz. I THINK it should produce 28.8 sps when configured for 40Ksps at a clock freq of 7.37MHz. The MODE0 register is set to 0x83. This should satisfy the 10000 - 11111: 40 kSPS (fCLK = 10.24 MHz) . It is producing DRDY- at a 35.5Hz rate. The setting of 3 in bits 2:0 seems to select sinc4. No setting for sinc5. But maybe 40,000 setings produce sinc5 filtered data.

We want the sinc5 data with the first notch at the OWR of the filter. With an external clock of 2.048MHz we expect (and are told by TI) that this is a valid configuration.

Can anyone help?

Thanks

Terry Johnson

Consulting Engineer