I have a design that uses four ADS7947. All converters are sharing a common clock and CS. There is an FPGA generating the clock and CS signals and reading the individual SDO. Usually it works very well, but once in a while the converters do not produce data. The symptom is that SDO is stuck low on all four converters. I suspect that the FPGA has come up in an unexpected state and put the converters into limbo, perhaps 32b mode. However, I tried clocking the chips with CS high, and that is not sufficient to recover. If my guess about 32b mode seems right, can you clarify how to get out of that mode ?

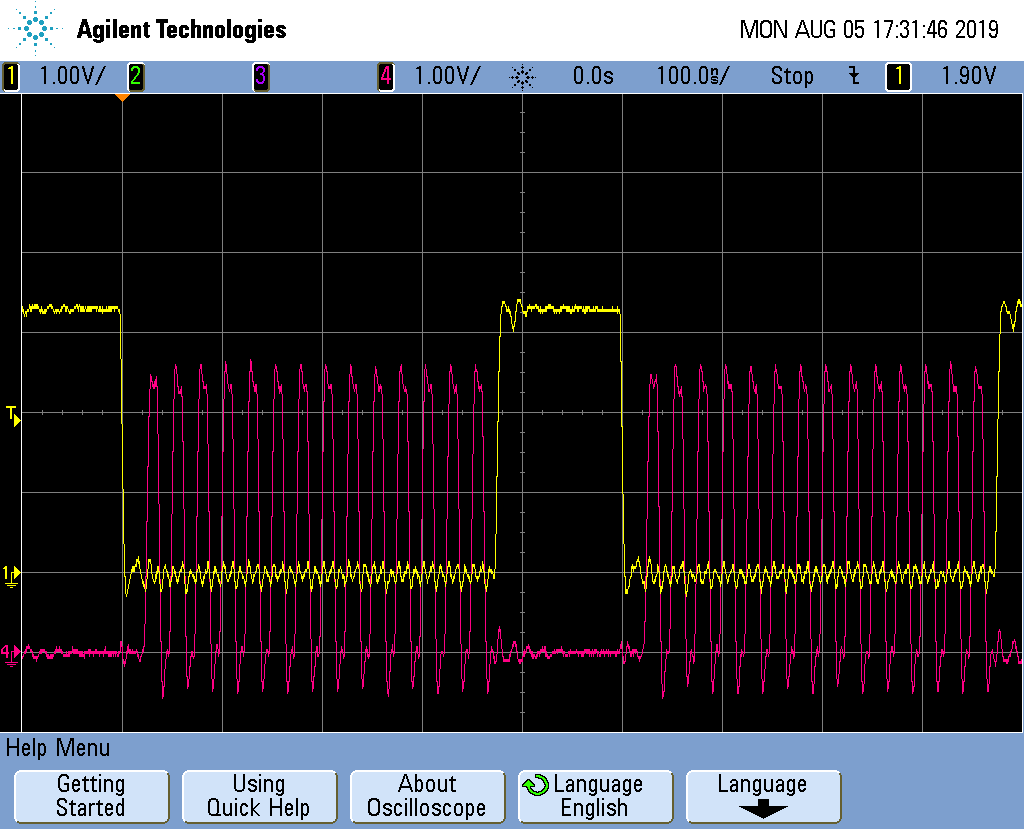

Here are some more details about how the parts are being used. The clock is 40 MHz with 50% duty. CS is low for 380ns and high for 120ns. The clock idles low, then it is pulsed 14 times after CS is asserted. CS rises after the falling edge of the 14th clock. I have checked the timing against the datasheet and don't see any violations. Also, the signals look clean without significant overshoot or ringing.

PDEN, CHSEL, AIN1N and AIN1P are not used and tied to ground. The part is used with AVdd=5V, DVdd=3.3V, Vref=4.096V