Other Parts Discussed in Thread: ADC16DX370

Dear Supporters,

I am working with a custom integration of Arria 10 SoC Dev Kit with Abaco FMC144.

Clock generation and A-to-D conversion are performing OK, but no luck yet with the JESD link to the DAC38J84.

SYSREF is a 2-pulse train at 1/32 the frequency of DACCLK, which is 148.5MHz.

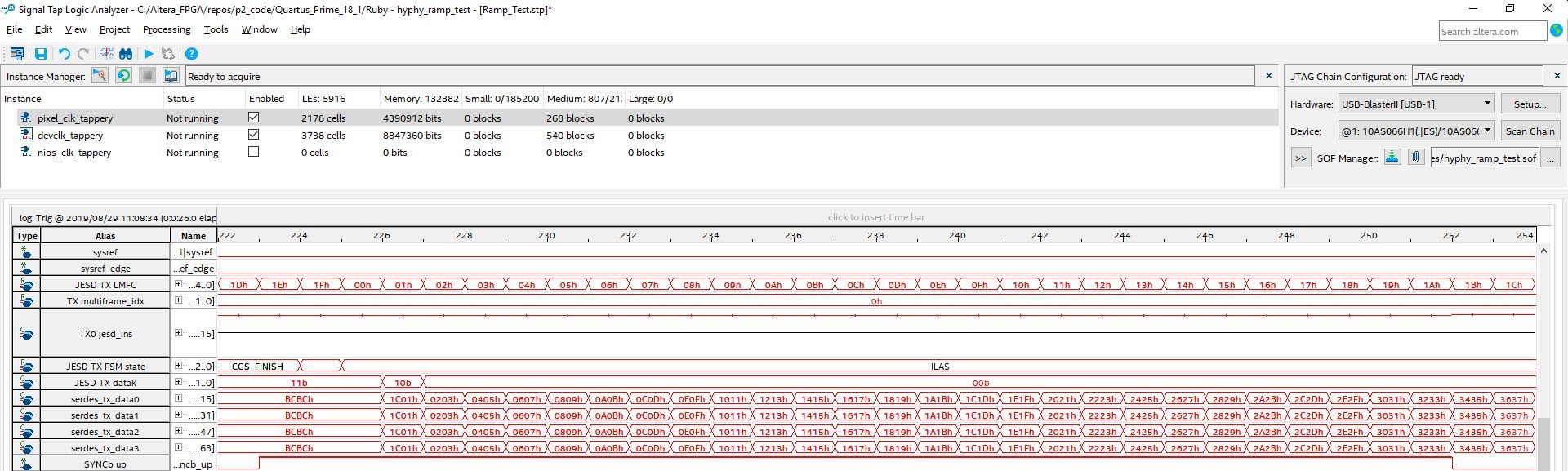

K = 32 in our setup, LMF is 442.

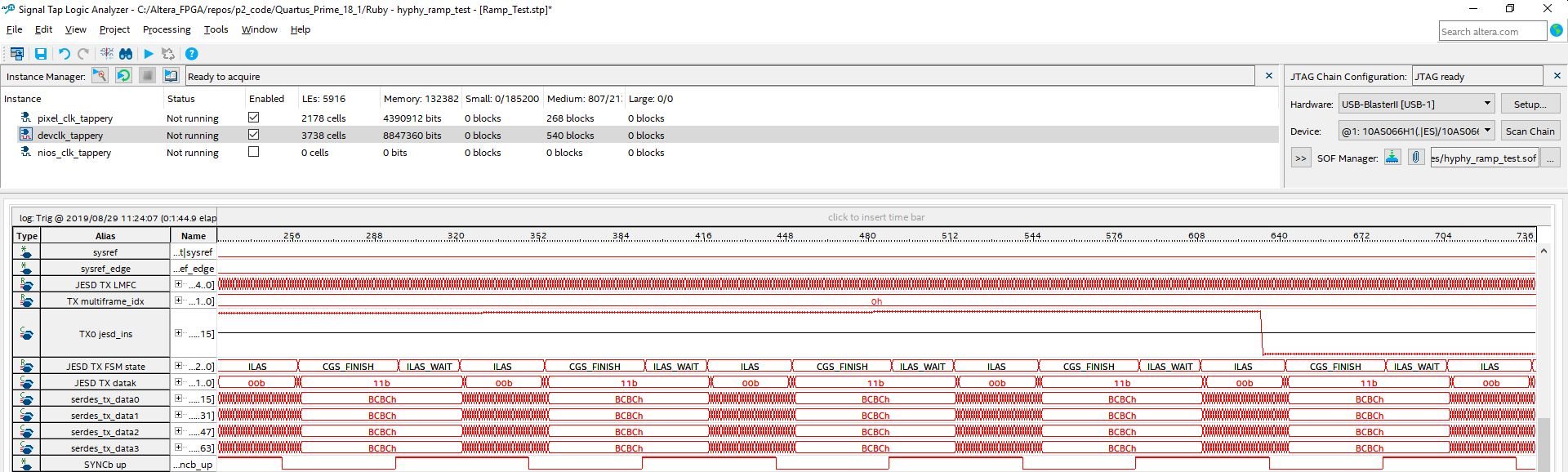

SignalTap shows that the JESD link with the DAC chip is briefly established, but then this behavior repeats indefinitely: the DAC chip asserts SYNCb, then deasserts SYNCb after receiving a sequence of K28.5 symbols, but then reasserts SYNCb at varying points during the ILA sequence, usually in the 3rd multiframe. A snapshot of the lane alarms taken just after the SYSREF pulses shows only Frame Alignment error in 1 or 2 lanes, while the other error flags are clear.

Based on a prior thread, I have tried clearing 0x51[7:0], which should suppress any error from triggering SYNCb. However with this setup, SignalTap shows SYNCb to be illegally asserted for short durations.

Can you please provide some insight as to what causes this SYNCb behavior?

Hopeful thanks --todd