Other Parts Discussed in Thread: SN74AVC16827

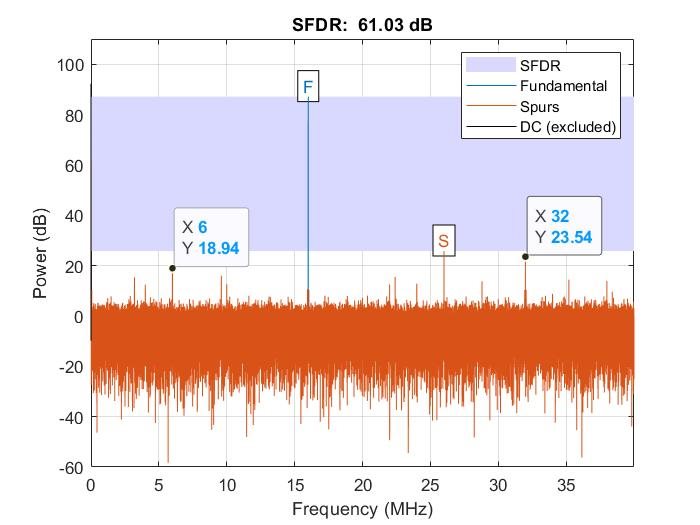

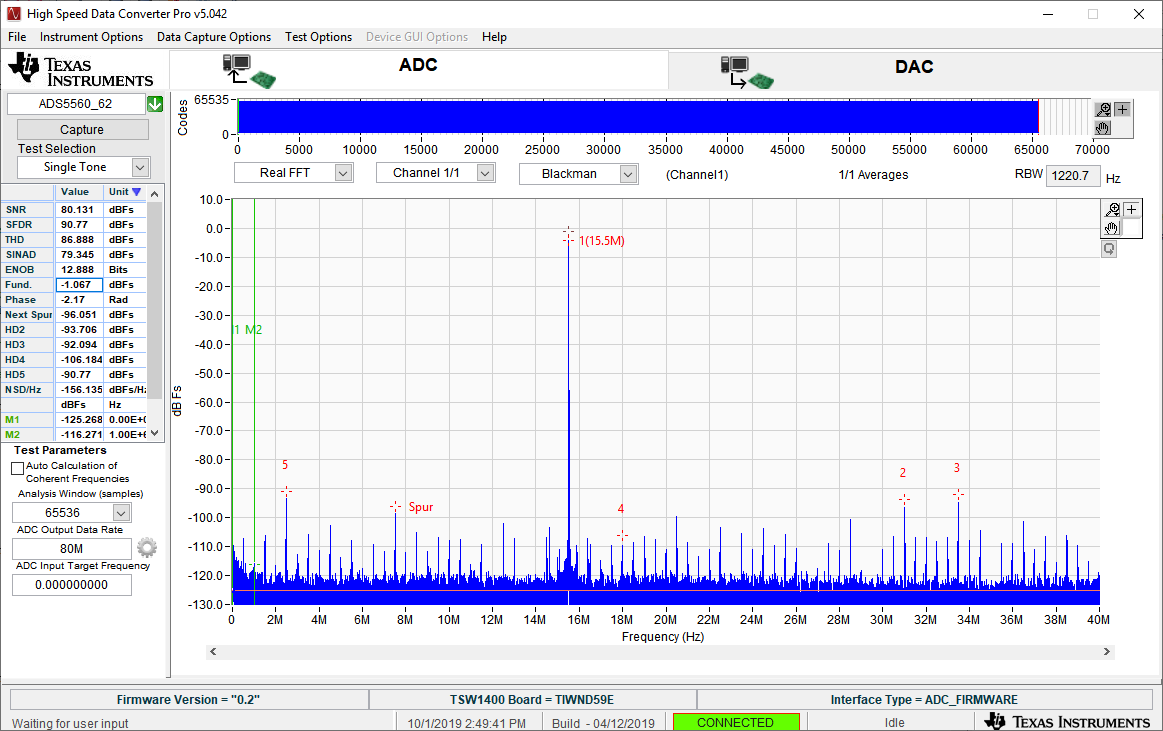

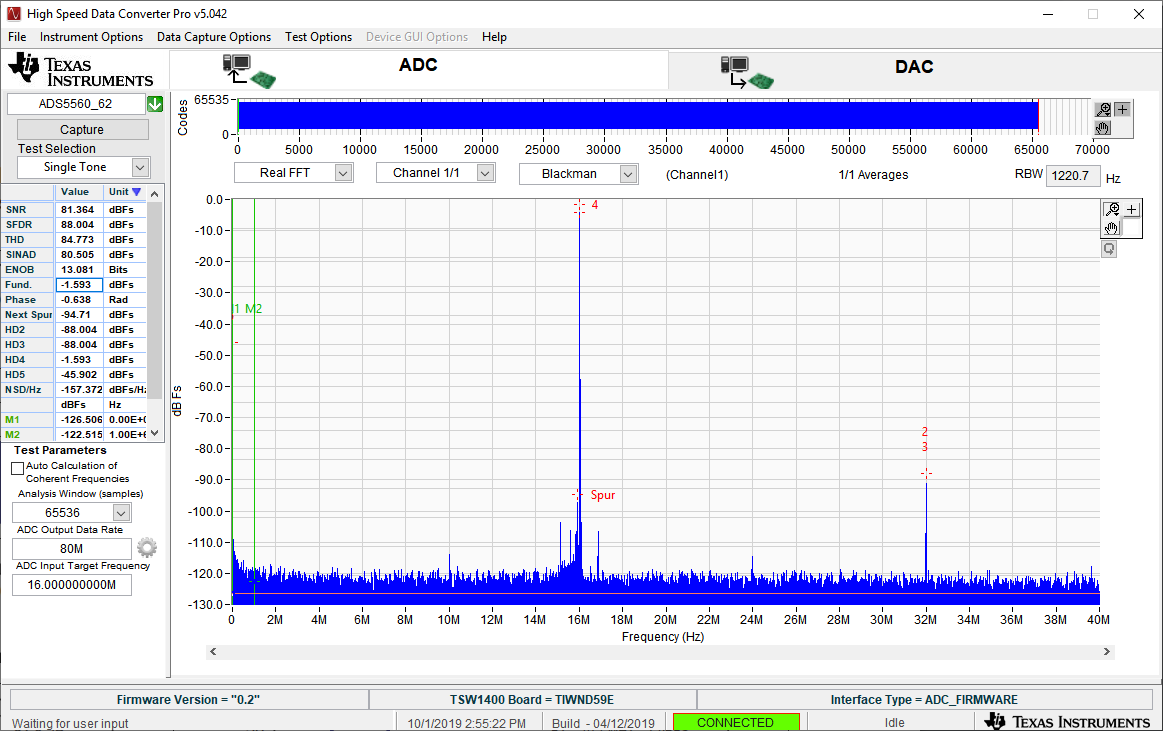

The measured SFDR is 48dBc as compared to 84dBc expected from the datasheet due to harmonic spurs. The input sine wave frequency of 16MHz and the clock frequency of 80MHz were applied to ADS5562EVM board with added LVDStoCMOS converter on U15. The measured SFDR plot is attached.