Other Parts Discussed in Thread: ADS54J60

Hello,

My customer have a question about ADS54J42.

[Q]

They are evaluating ADS54J42 on their board.

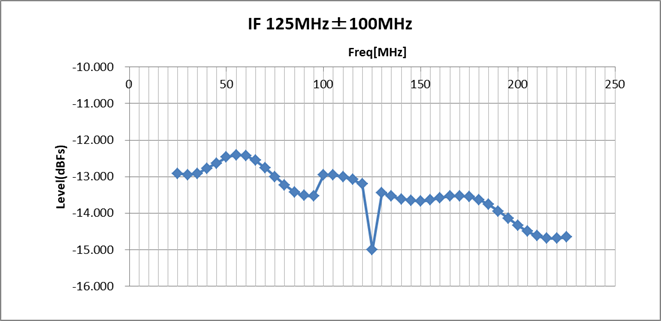

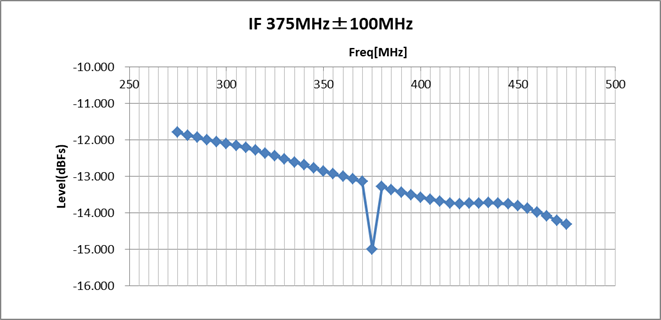

The issue is about 2dB lower when the input frequency is 1/4*fs or 3/4*fs.

Their sampling rate is 500MSPS.

The following is the evaluation results.

I think this is due to the interleaving block and the setting.

Do you have a way to avoid this issue ?

Best Regards,

Hiroshi Katsunaga