Hello,

I have a question about ADS5562.

<Customer Use Case>

- Sampling frequency: 12.5MHz

- LOW SPEED mode (Tying the SCLK pin to high)

- CMOS mode

[Q1]

Their CLKOUT (5pin) duty cycle is not 50%.

Their measurement result is about 78%.

Why is this?

Are there any possible causes for the above?

- D/S, p15, 6.11 Timing Characteristics for LVDS and CMOS Modes

PARALLEL CMOS MODE: CMOS output clock duty cycle= 50%

<My thoughts>

The measurement conditions for the following data are Default Speed Mode.

I think that it may not apply when used in Low Speed Mode.

The important thing about CLKout is not the duty cycle but the rising edge.

Therefore, I don't think I need to worry about the Duty Cycle not being 50%.

[Q2]

I asked them to investigate the waveforms to see if they met the following conditions:

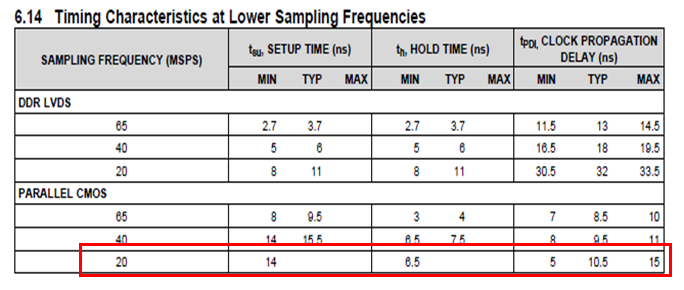

- D/S, p16, 6.14 Timing Characteristics at Lower Sampling Frequencies

- D/S, p18, Figure 5. CMOS Mode Timing

As a result,

tPDI = about 70ns.

tsu = about 25ns

th = about 55ns

This result does not seem to meet the requirements.

Why is this?

Are there any possible causes for the above?

Also, I think that even if the Output Clock Position is adjusted using the SEN Control Pin, the request cannot be satisfied.

What should I do?

Best Regards,

Kaede Kudo