I am attempting to configure the ADS8588S ADC with an Arduino Teensy micro controller. I am using the serial interface mode, using only DOUTA to read after conversion using the arduino SPI interface. I've included the pinouts for the teensy and the ADC below.

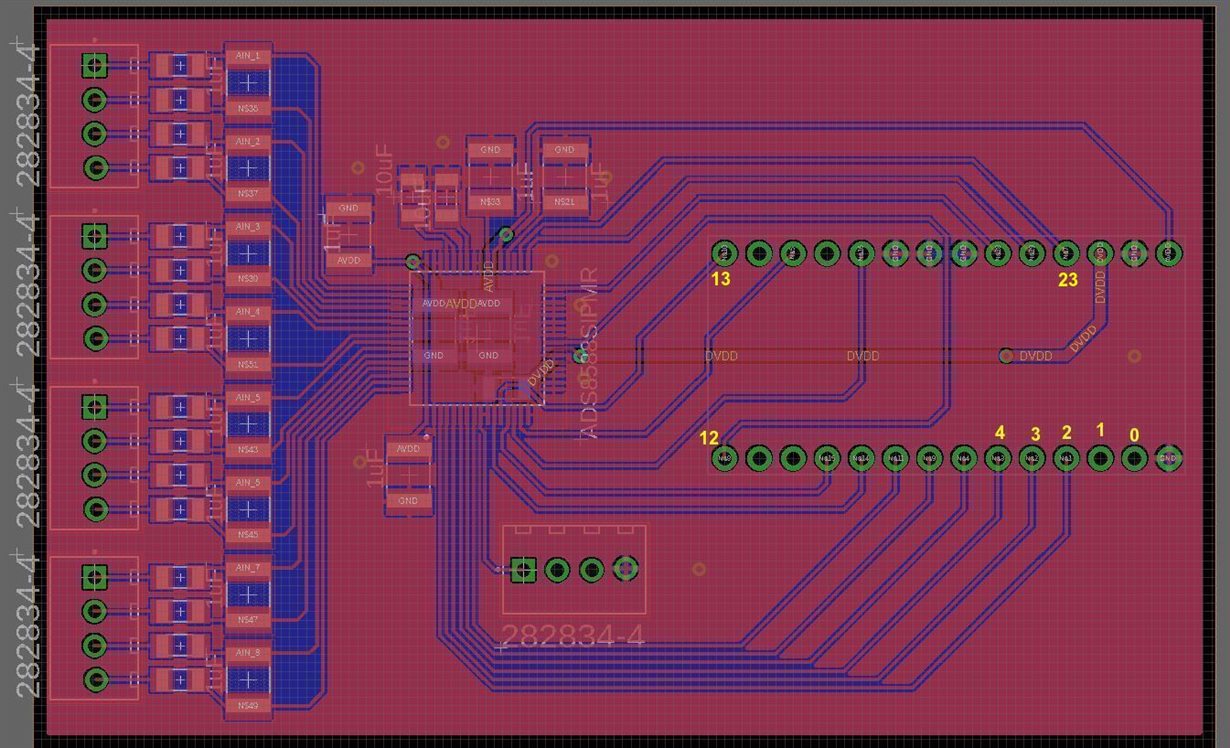

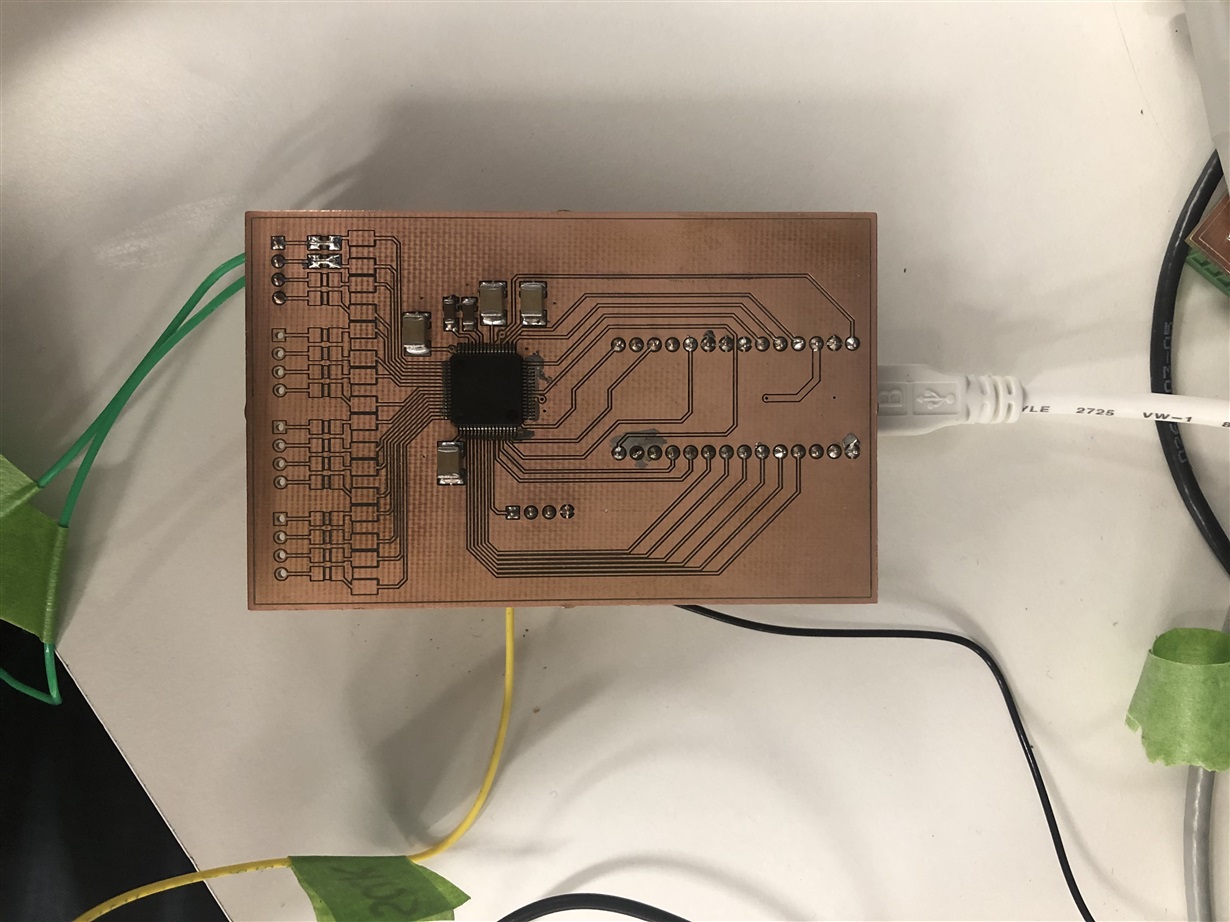

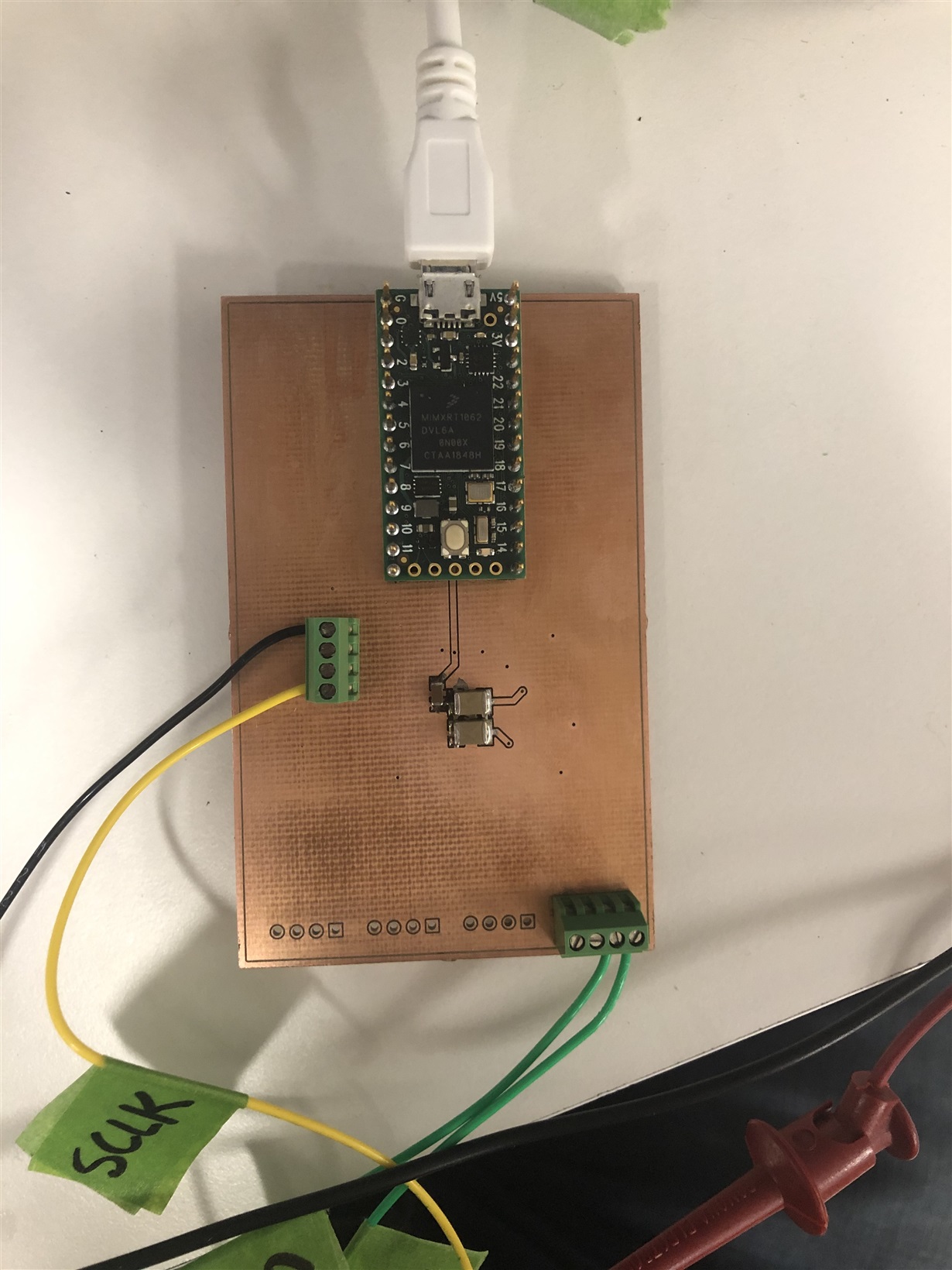

I soldered these two components to a PCB I designed. I've attached my schematic as well as pictures of my PCB. I labeled a few of the pins on the teensy, it is mounted on the underside of the schematic view. And the ADC is mounted with the marked corner in the bottom left, so rotated 90 degrees compared to the pinout shown above.

The yellow wire is connecting CONVSTA/B which are tied together, to an external 3.3V 50% duty cycle square wave.

I select serial mode with:

PAR/SER/BYTE SEL logic HIGH

DB15/BYTE SEL logic LOW

I've included my arduino program running on the teensy below.

I define clockspeed as 20MHz, but in reality it is 18.75MHz, 1/32 of the 600MHz teensy clock speed.

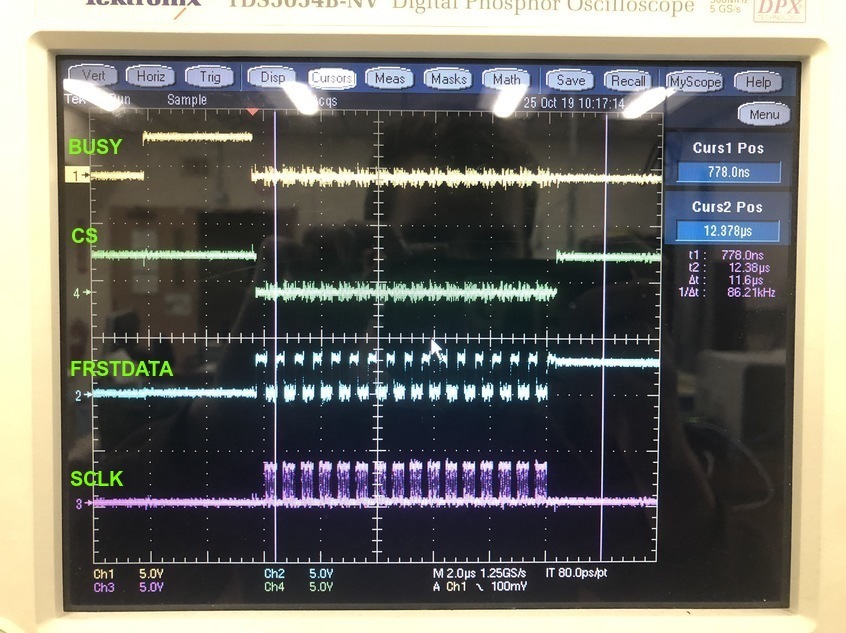

My issue is that the first byte is being sent 16 times, instead of being updated. This is also clear from the FRSTDATA flag which goes high 16 times. I think that FRSTDATA should stay high for the first 16 SCLK cycles only, but in my system it goes low after just a single SCLK cycle.

But BUSY, CS, and SCLK appear to be working fine. Also I did not include the external system clock tied to CONVSTA/B (yellow wire in earlier pictures), but it also works fine and rises just before BUSY goes high as expected.

The problem is also apparent in my data received, where all 8 interpreted values are identical. This is because the first most significant byte of channel 1 is duplicated for the other 15 bytes of data.

Could this be a hardware issue to do with grounding? From the timing diagram I notice that BUSY and CS appear to have some crosstalk with the 18.75MHz SCLK. Or do I have a software issue?

Thank you,

Skyler