Other Parts Discussed in Thread: ADS8555

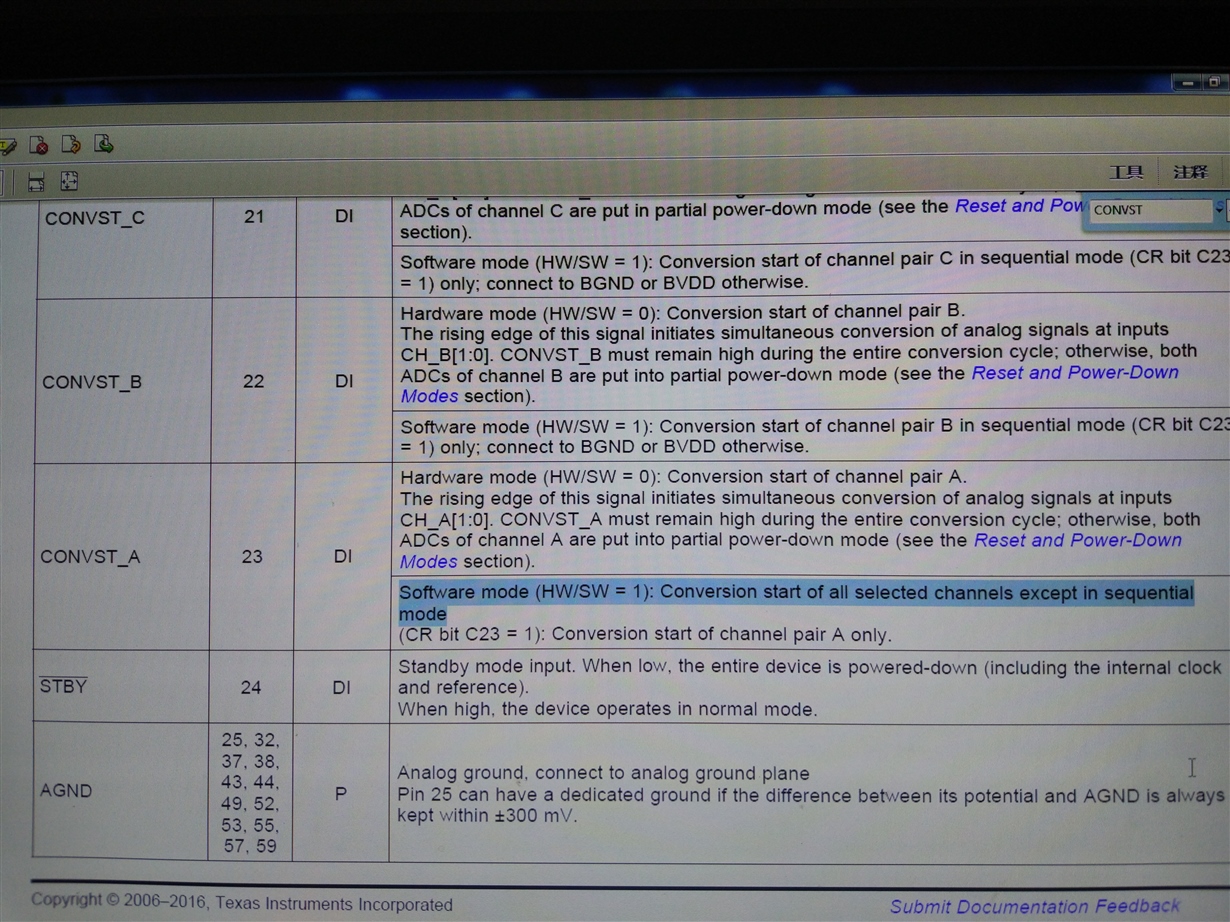

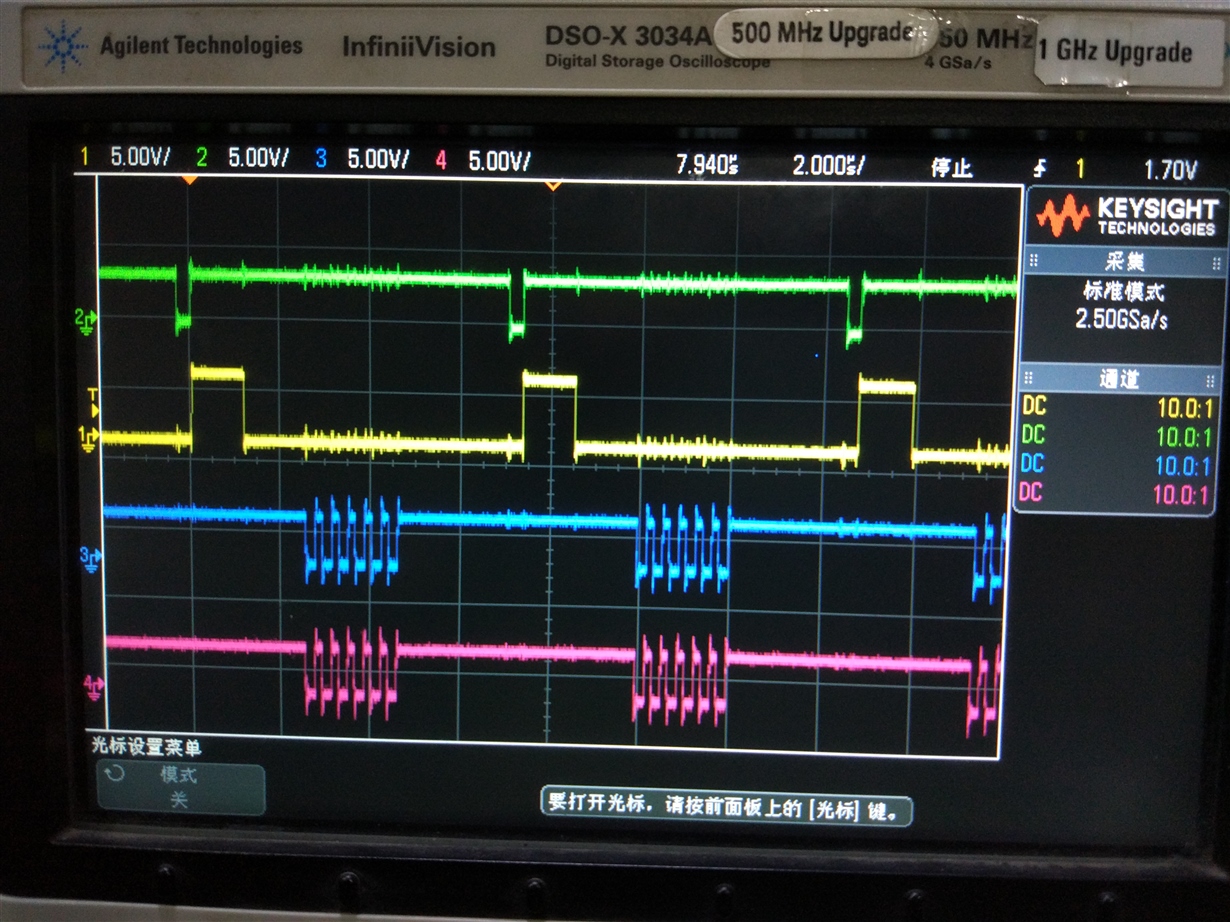

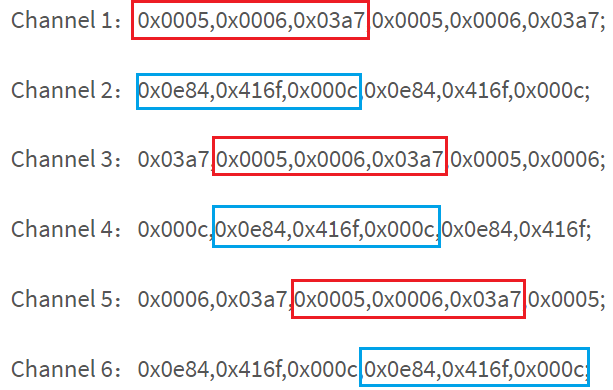

hi,from the datasheet,bring the convst signal low during an ongoing conversion when busy signal is high can put ads8556 into power-down mode. Is there any other reason can put ads8556 into power-down mode beside this?