We're developing an application where we want to sample the ADS9224 at 3MHz. Due to I/O constraints, we can only use a single data line per channel. This means we need to use a clock of 60MHz for clocking the data out of SDO-0/0A and SDO-4/0B. To do this reliably under varying delays, we want to use CRT-S-SDR as the protocol to clock the data out.

I'm running into a very strange problem while trying to get this to work. When using the following configuration, things work as expected:

PROTOCOL_CFG (2h) = 0x20 (select CRT with SDR)

CRT_CFG (4h) = 0x01 (select INTCLK for the STROBE output)

OUTPUT_DATA_WORD_CFG (5h) = 0x22 (mask READY output, output fixed pattern 0xA55AA55A)

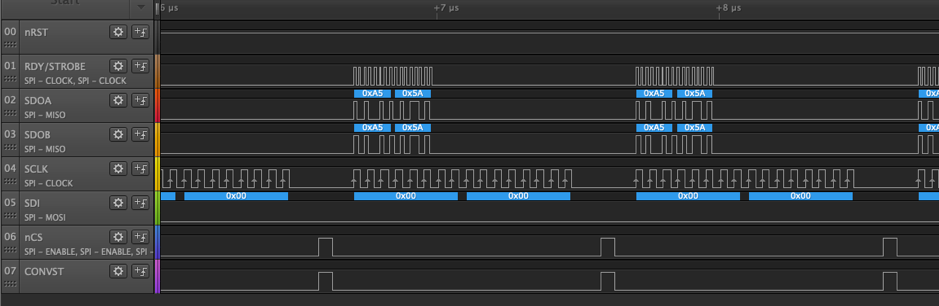

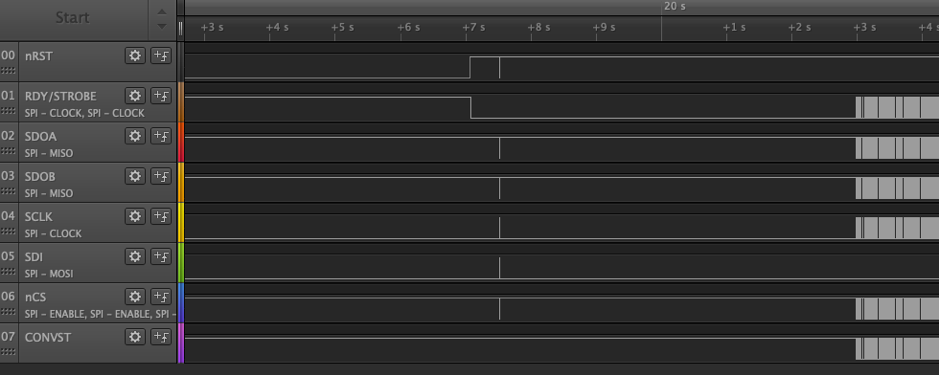

On my logic analyzer, the output looks as follows (note I'm still generating a SCLK even though it is not used), which is exactly how I would expect it. Note I'm running at 1MHz CONVST / 20MHz SCLK for now.

Now when I want to switch to using SCLK as STROBE input in stead of INTCLK, I change a single bit in the configuration:

PROTOCOL_CFG (2h) = 0x20 (select CRT with SDR)

CRT_CFG (4h) = 0x00 (select SCLK for the STROBE output)

OUTPUT_DATA_WORD_CFG (5h) = 0x22 (mask READY output, output fixed pattern 0xA55AA55A)

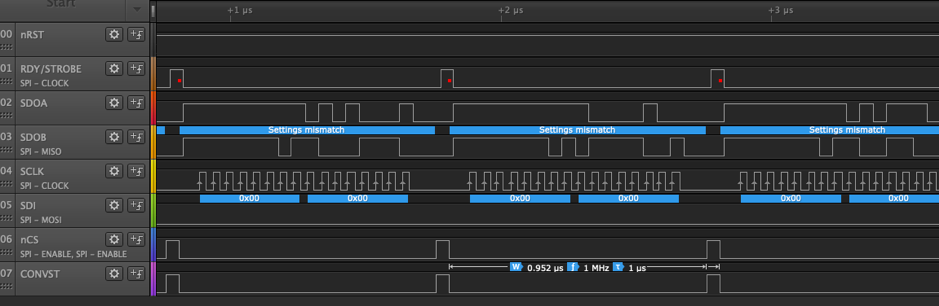

However, now it seems the ADS9224R is completely ignoring all of the configuration, and running at its default configuration of using SPI-00-S-SDR, not masking the READY output, and not outputting a fixed pattern:

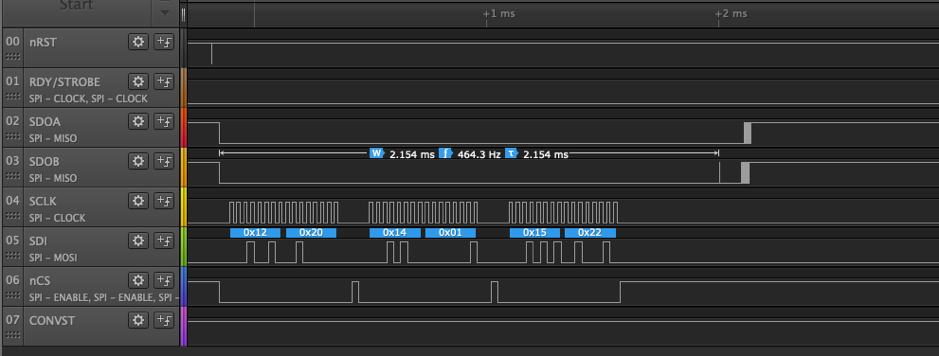

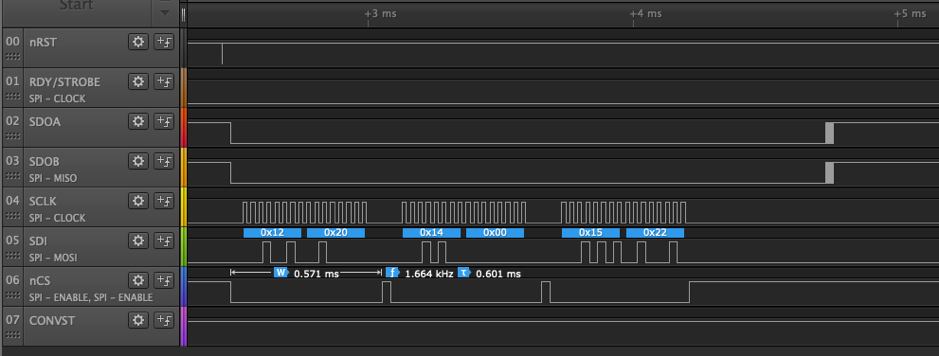

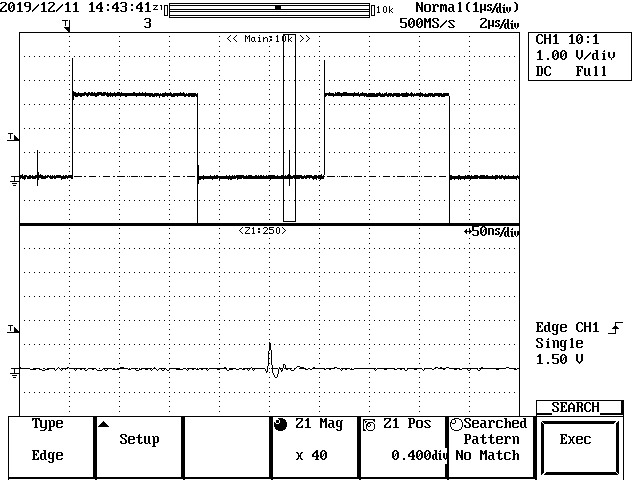

Even though only a single bit has changed in the configuration. For reference, here are the captures of the configuration step (the first at the top, and the second at the bottom):

Note that I toggle nRST just before the configuration step to clear the existing config. The pulse is 450ns long, and there is 33µs between the nRST pulse and nCS being pulled low to send the configuration. Also note that the configuration clock is very slow, being only 33kHz.

The glitching of the SDOA/SDOB lines at the end is probably an artifact of the fact that these lines become floating (high Z) when nCS is set high.

The total startup sequence looks as follows:

Any ideas on what's going wrong with the configuration? How can changing a single bit in the CRT_CLK_SELECT field make the ADC ignore the configuration completely? Any help would be greatly appreciated.