Other Parts Discussed in Thread: REF3125

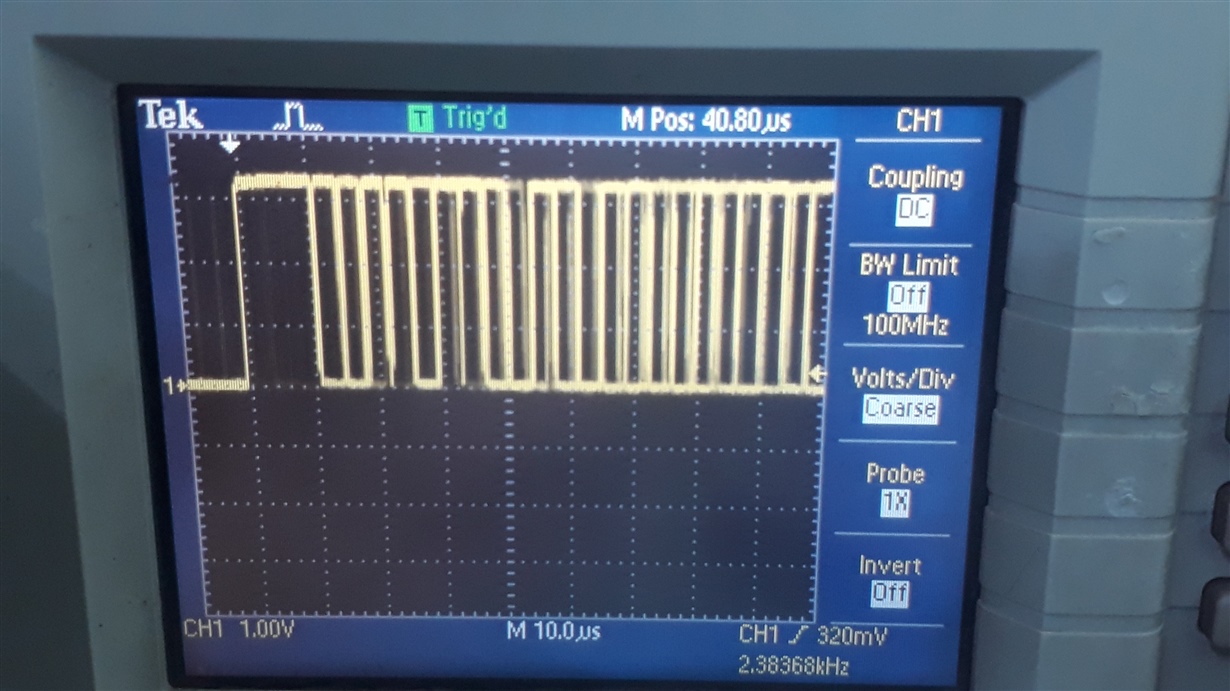

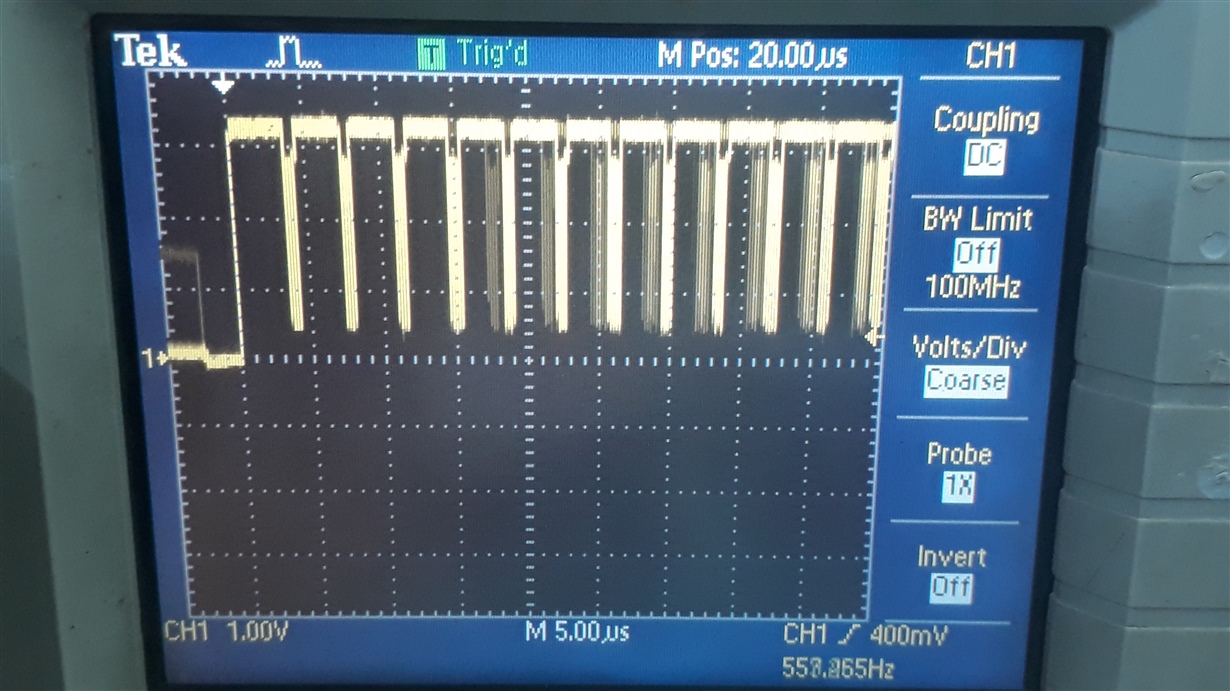

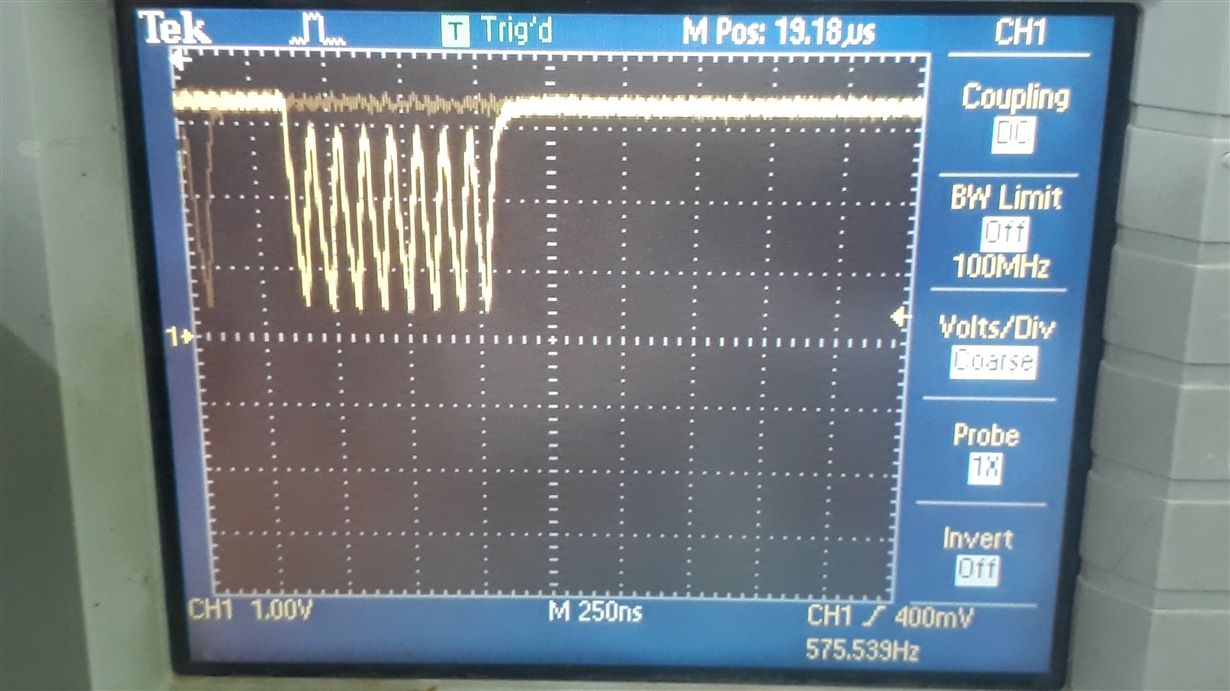

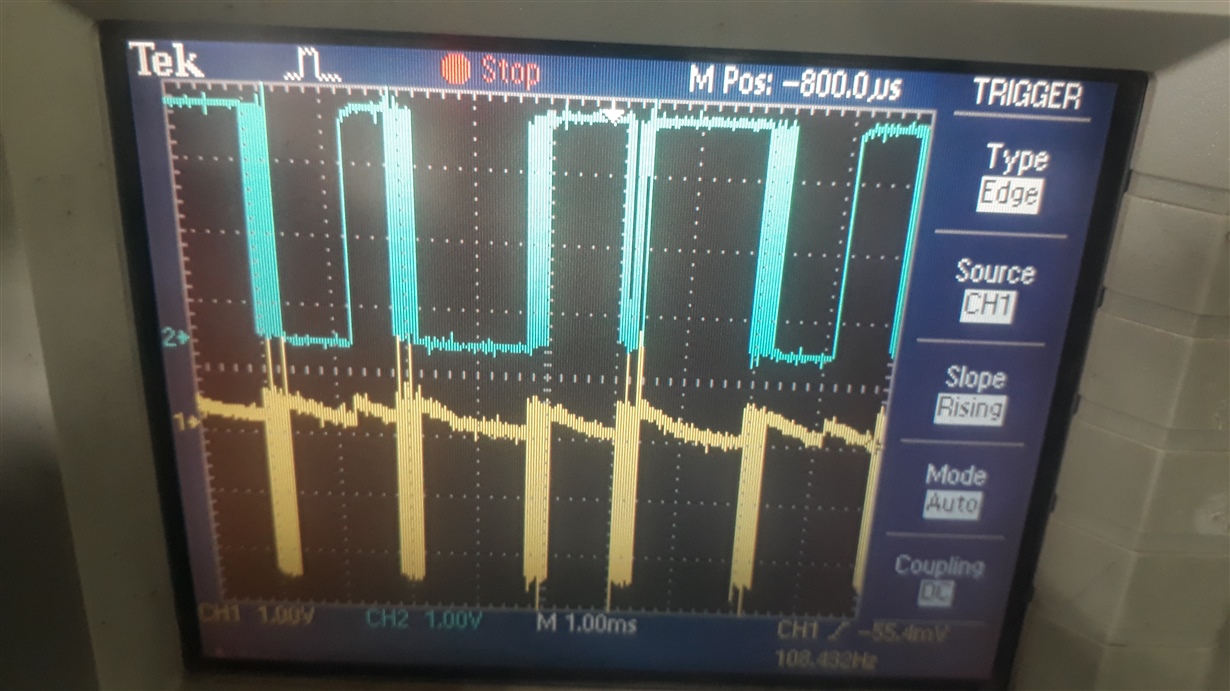

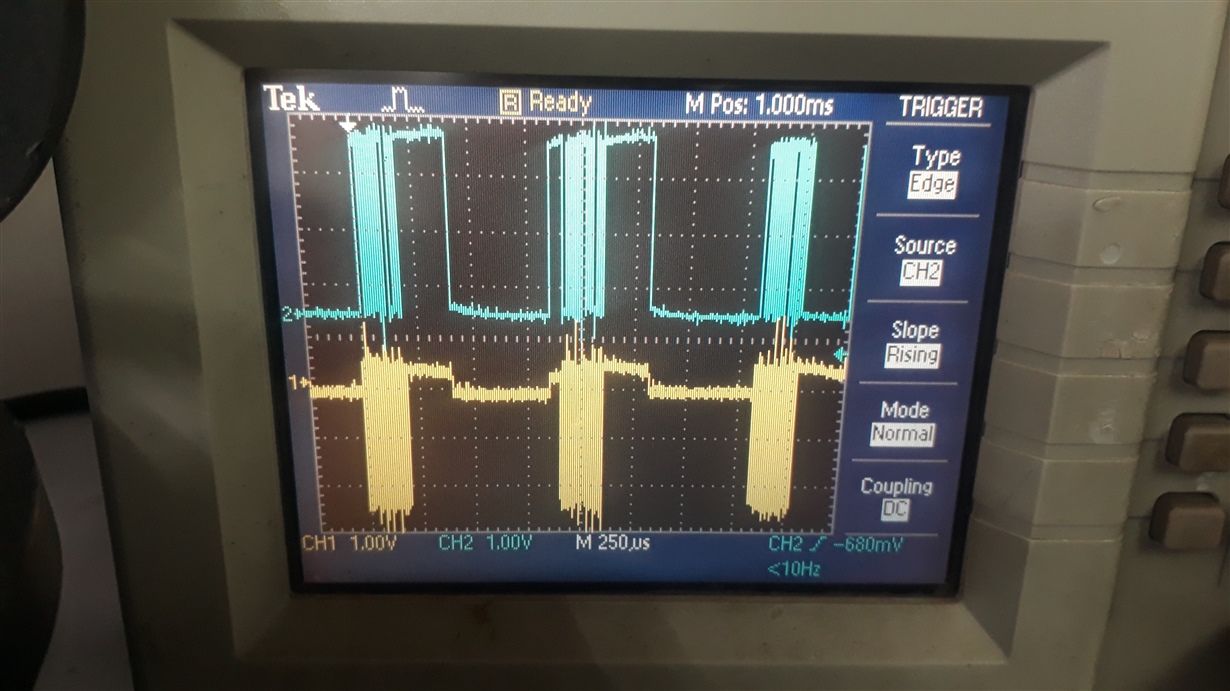

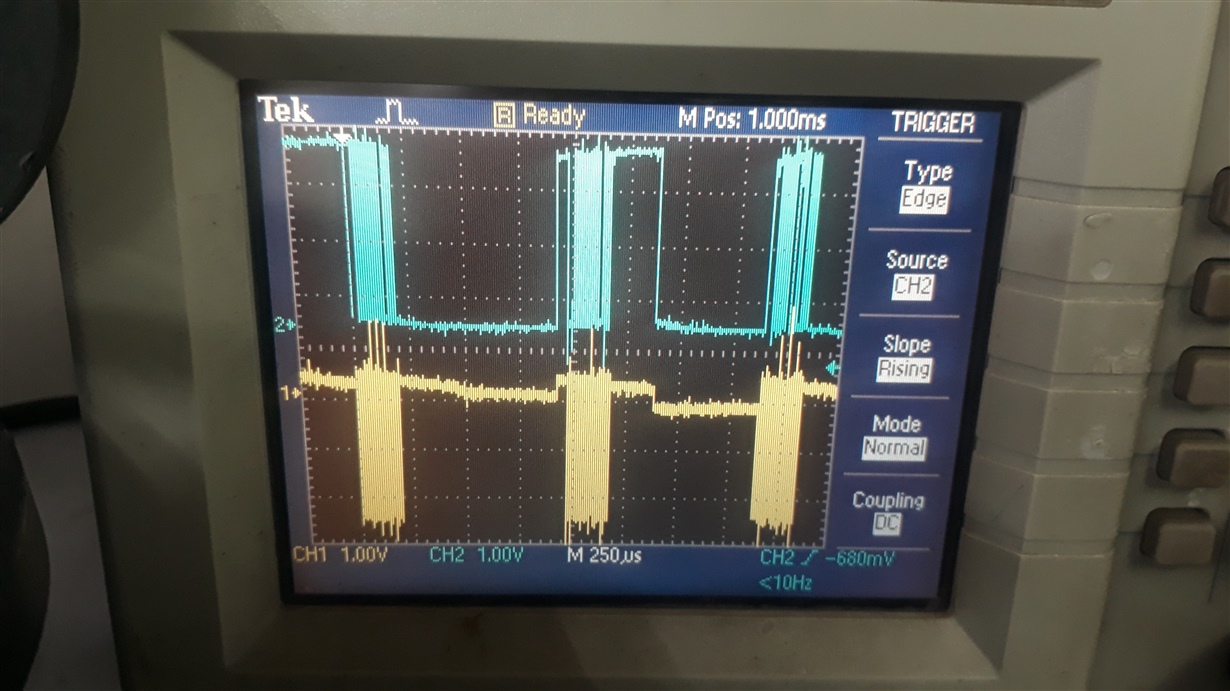

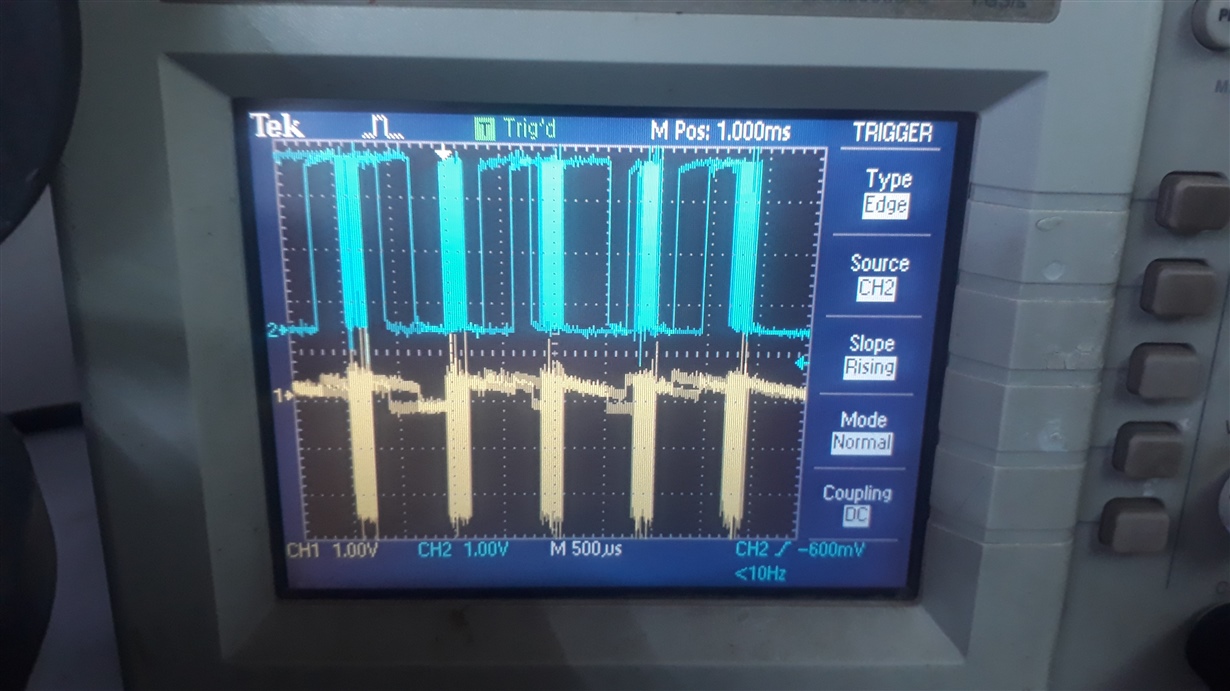

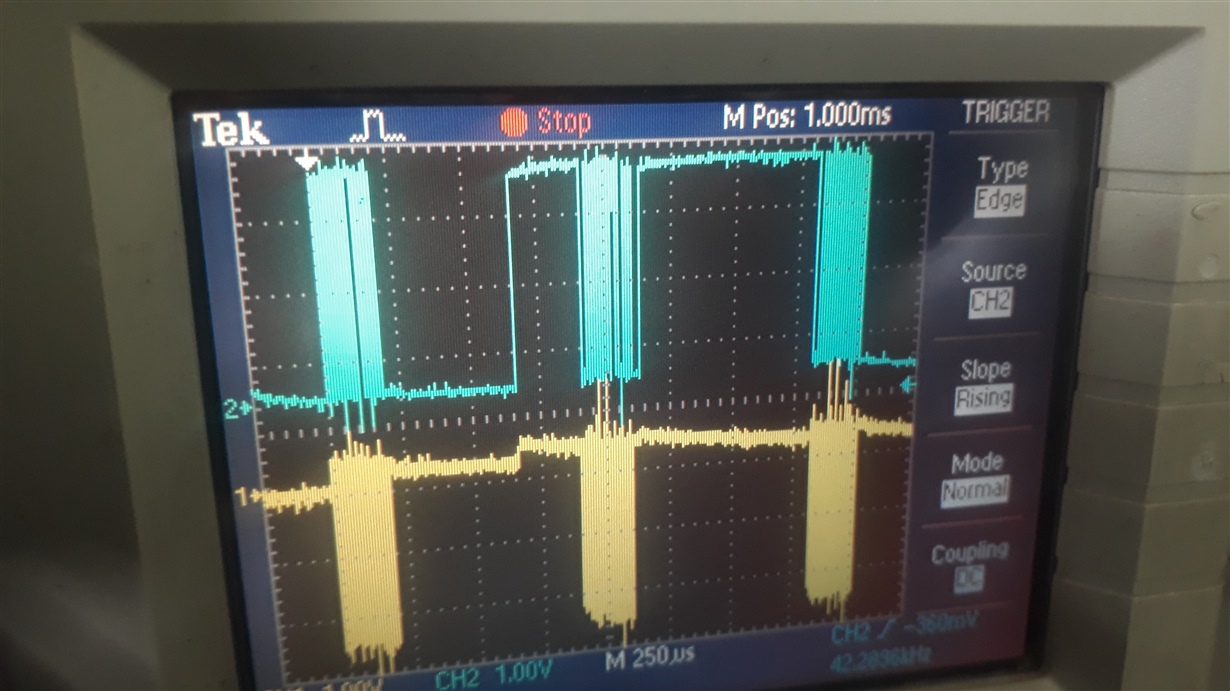

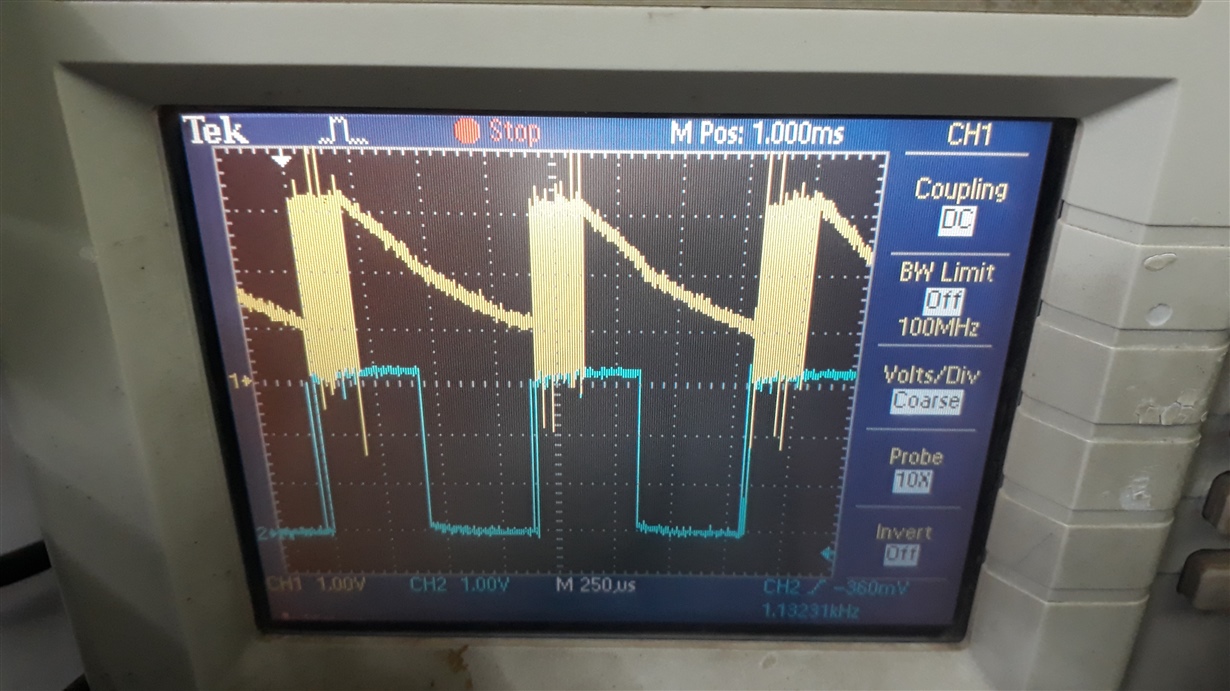

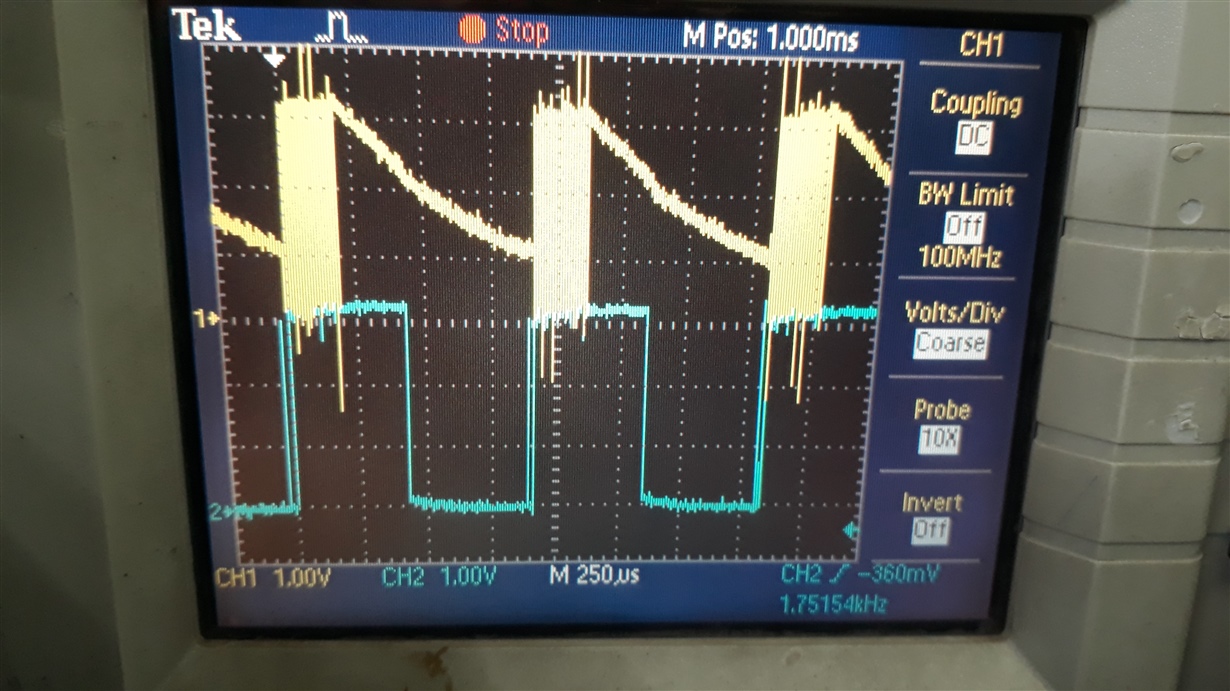

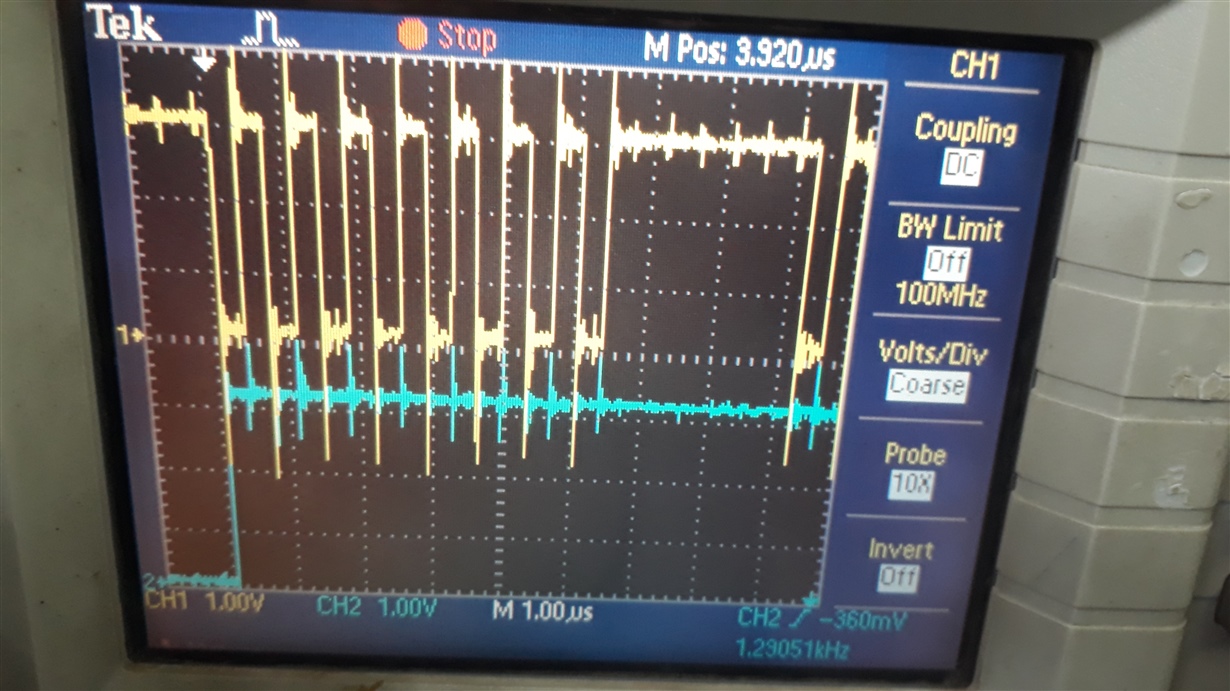

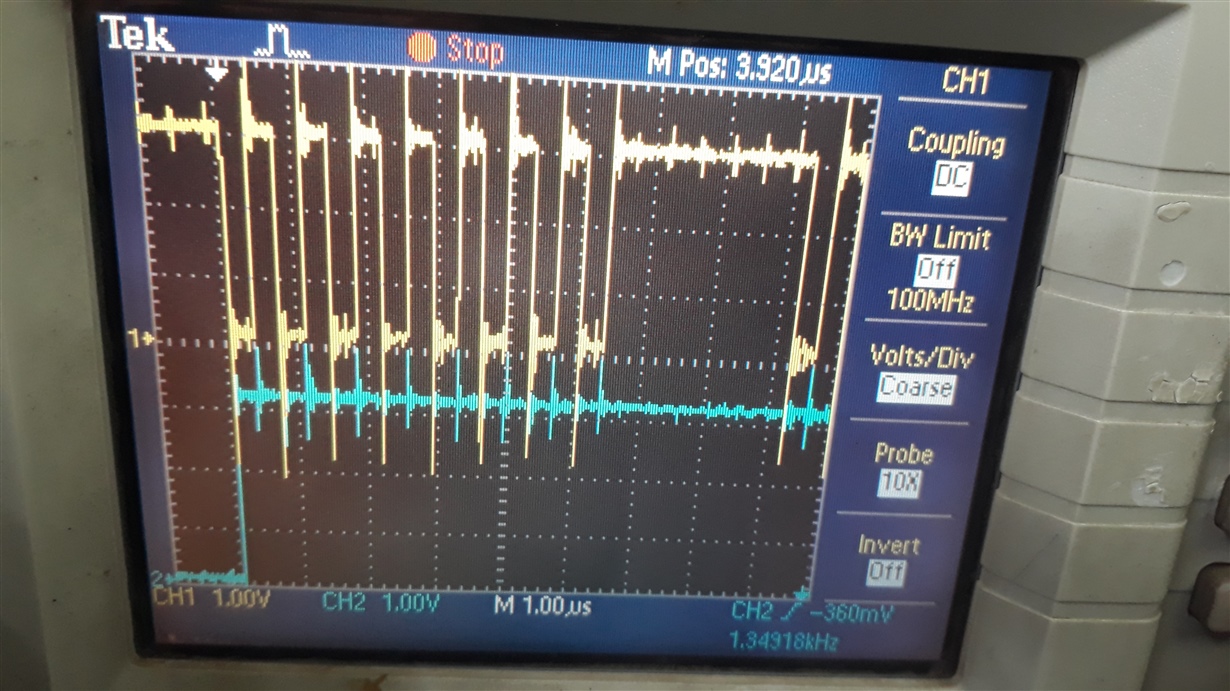

2 ADCs are used is daisy chained configuration

Mode: Low speed

CLKDIV: 1

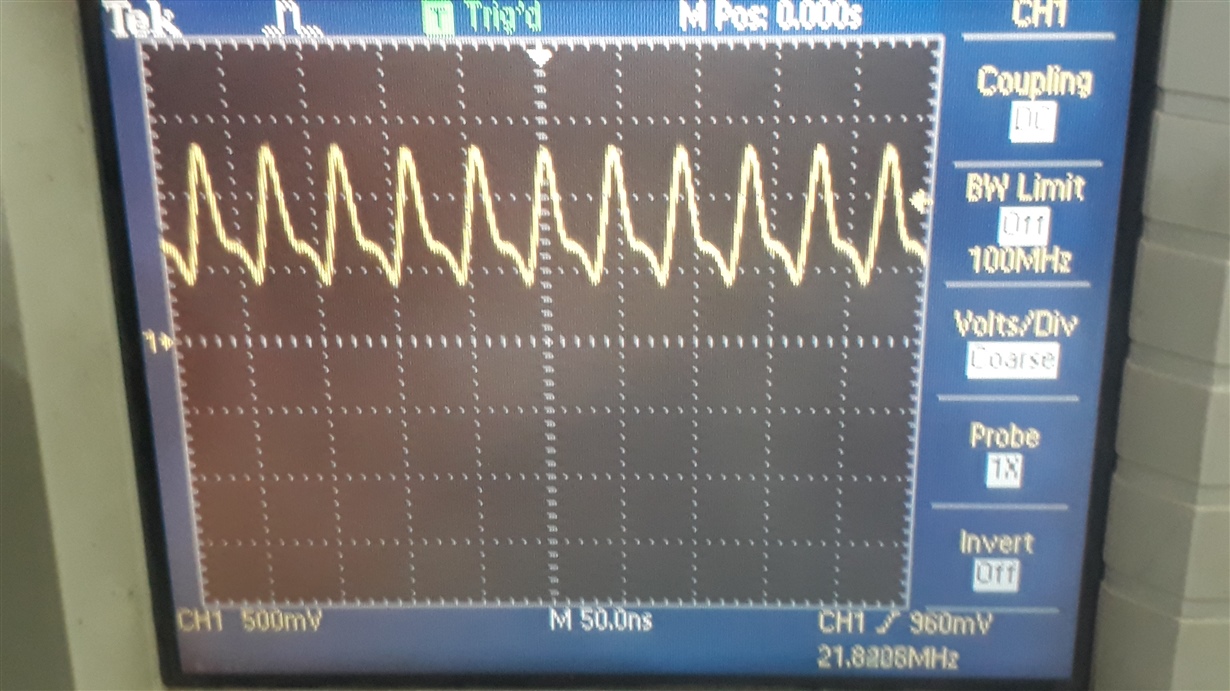

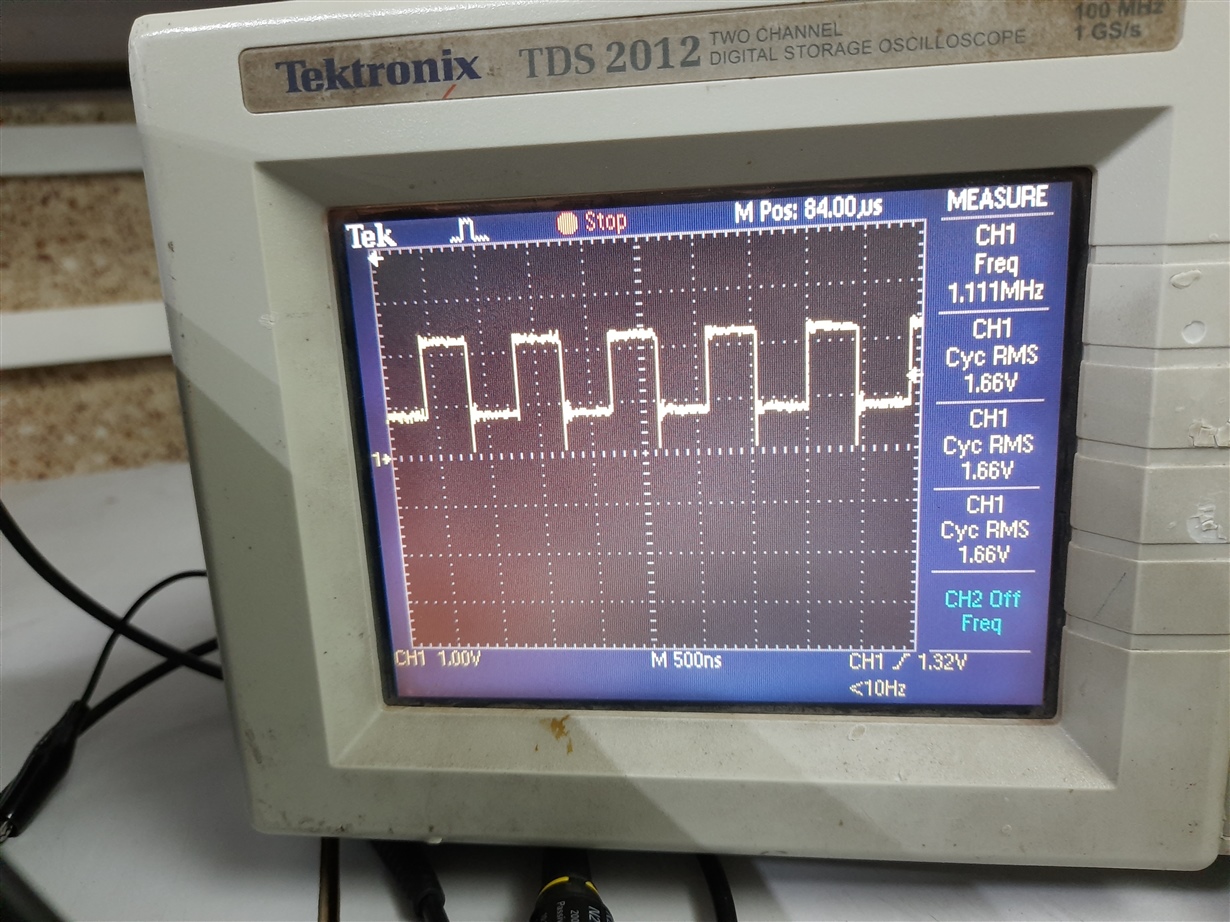

Fclk: 4.2MHz

Sclk: 2.56MHz

Data output format: SPI TDM Fixed

These are the settings, but we get only 15 samples per second(for each channel)

DRDY pin is polled for data ready

We need higher SPS, what can be the solution for it ?