We are using the AD1240 in a measurement system that requires very good rejection of differential mode mains noise (50Hz/60Hz and harmonics).

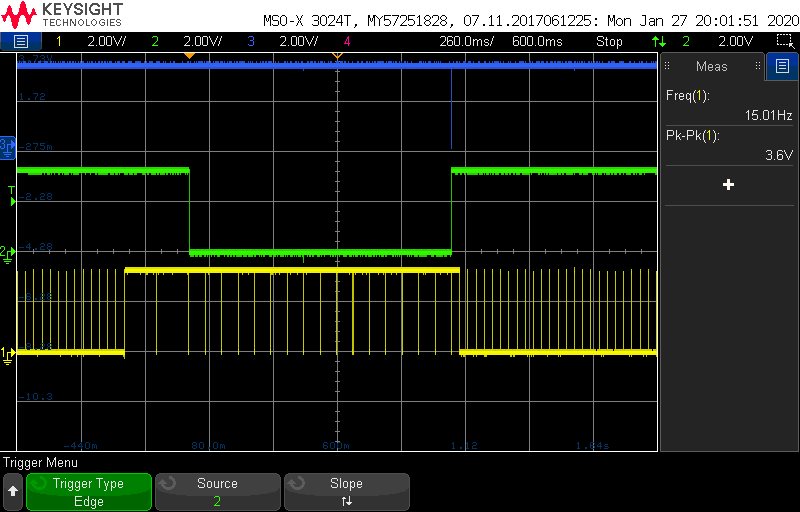

Ideally, the converter would run continuously at a data rate of 15Hz - we have tested this and rejection of mains frequencies is excellent.

If the the converter runs at 7.5Hz then changes to 15Hz how long must we wait until we get the correct filter response again?