Hello,

We are using two ADS131A04 as a chain in Synchronous Slave Mode, CRC disabled, 24 bits, Hamming code off, and a free running SCLK (7.8125 MHz).

We are using an internal reference, AVSS -2.5 AVDD 2.5 IOVDD 3.3

Tested input signal is 1kHz sine wave with 2~3V pk-pk (0 to 2~3)

We have the same schematic as in the ADS131A04EVM.

We are not getting any data out after enabling the ADCs, and we did most of the configurations as in the datasheet so we are not sure if we missed a step.

The following register configurations were done:

A_SYS_CFG (0Bh) - 68h

D_SYS_CFG (0Ch) - default

CLK1 (0Dh) - 82h

CLK2 (0Eh) - default

ADC_ENA (0Fh) - 0Fh

and the rest of the user configured registers were left at default.

This is the following commands that we did to enable the ADC, the commands were done one after the other and their response was checked with the datasheet before doing them all at once.

UNLOCK

WREG 0D 82

WREG 0B 68

WREG 0F 0F

WAKEUP

LOCK

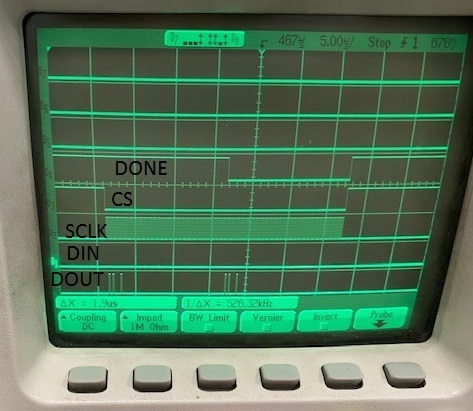

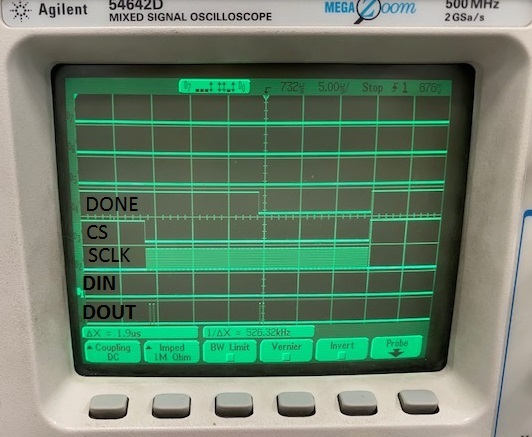

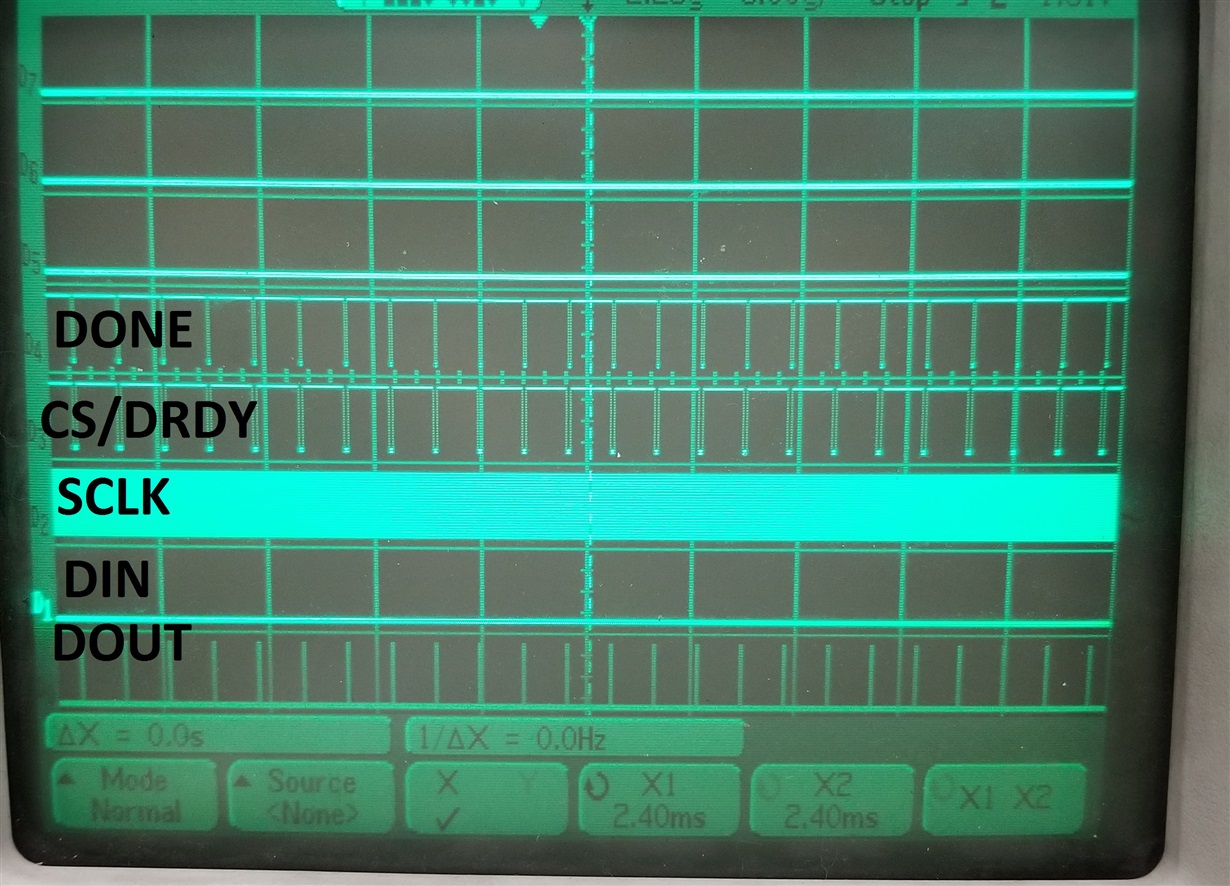

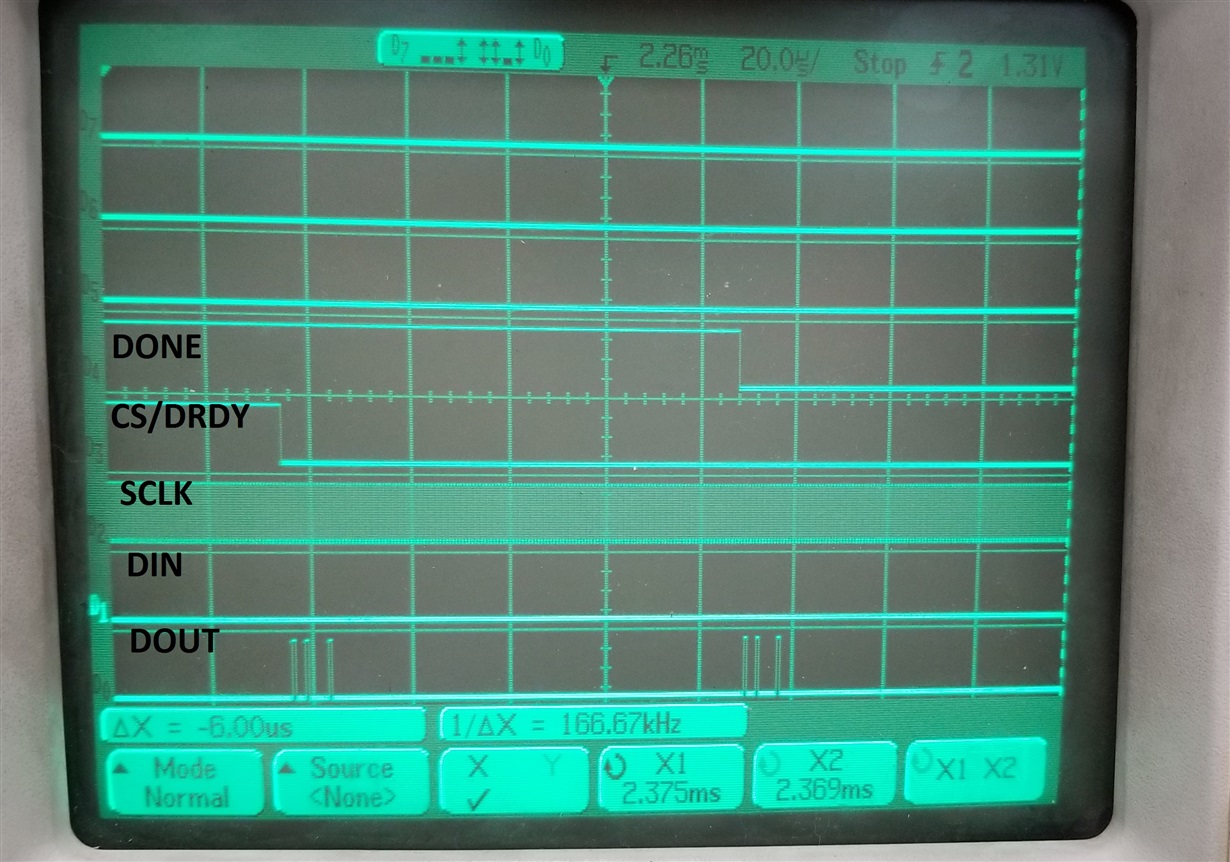

The following pictures show what we are getting from the scope, we got some fault for /DRDY but not as frequently which is why we are not sure if this is the sole problem

and this is what we got:

We checked all the registers to make sure we are configuring them correctly, and all gave us back wanted results. both DONE and CS/ /DRDY frequencies match.

Do you have any idea what the problem might be? We had a problem previously for not getting a response from the second device, but the problem was fixed by sending the command after the DONE goes low for the second device.