Part Number: TSW14J56EVM

Hello,

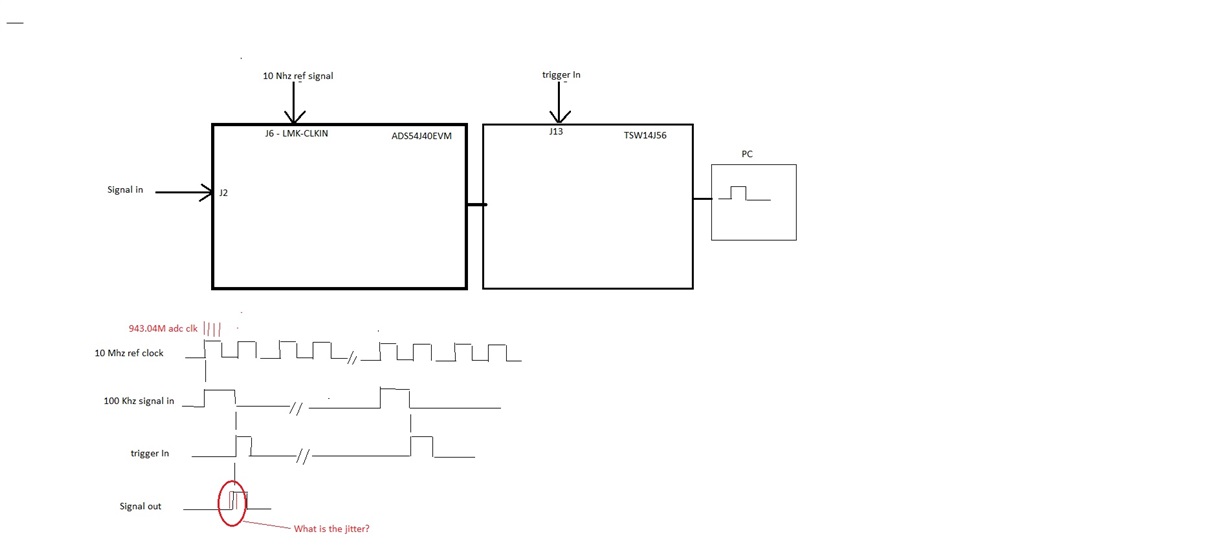

I have some questions concerning working with TSW14J56EVM board connecting to ADS54J40EVM board.

1. I want to sample only one "frame" of 1 Giga Pixels (using all the memory of one connected ADC) by using one shot trigger connecting to

J13 ( TRIG IN) on the board and be able to read all the 1 GPixels. (Working like a single trigger Scope).

2. Using the board normally (no outside triggers) I can only read 65000 points. The memory is 1 G points per ADC. How can I read them all.

3. Is it possible to give a sequence of triggers let say - 100000 - 10 us apart and then read the 1 Giga points. ( 10000 points at 1 Ghz sample rate for an interval of 10 us for 1 Sec.)

Regards,

Giora