So I am specifically wanting information for a HART application.

The datasheet doesn't cover the registers very well. For example, when the chip determines there is a GAP error - what exactly does that mean? Having this answer would be nice, but that's not the only query. None of the registers have a very good explanation.

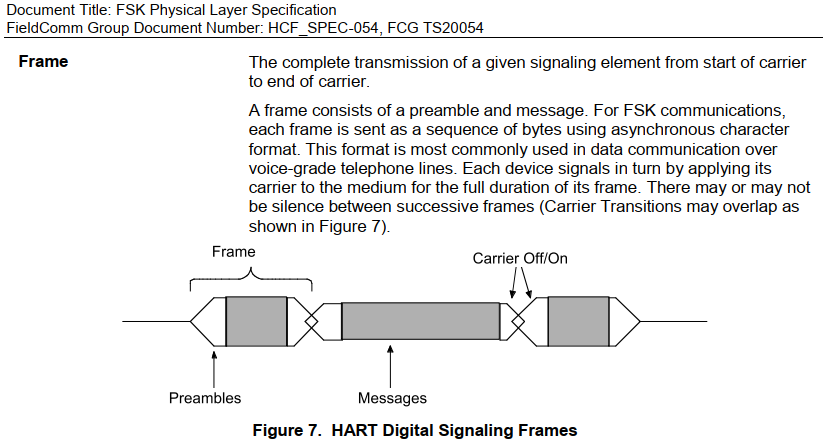

A second specific question is about the CD (Carrier Detect). I read that HART frames can overlap. If that is the case does the CD ever go inactive where the frames are overlapping? If so what are the specific conditions that the chip is using to generate the CD?

Mike.