MCU is STM32L4R5ZI No operating system - bare metal

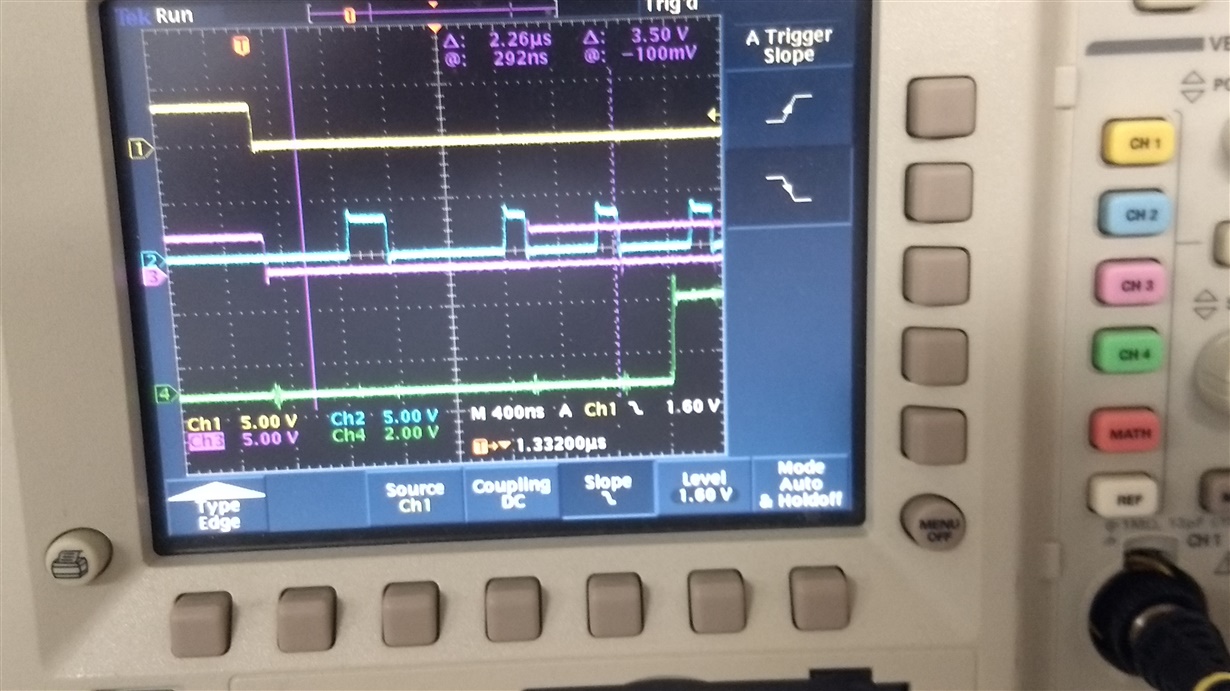

Manipulating GPIOs directly, (not using SPI block in the ST Micro MCU on our board)

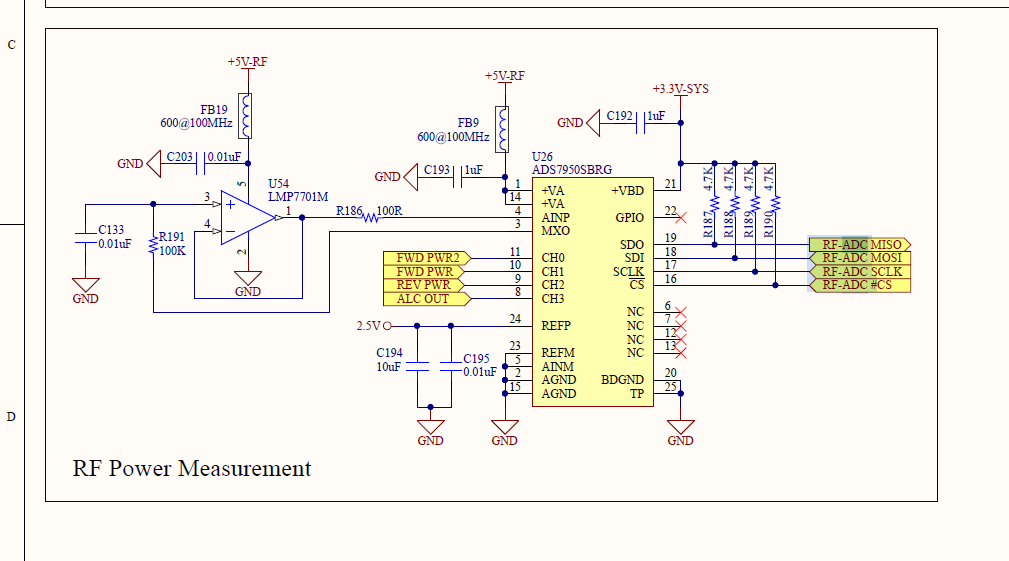

- REFP Analog reference voltage input 2.5V

- CH0: 0.229V

- CH1: 0.341V

- CH2: 0.356V

- CH3: 2.440V

dataIn:

- #define ADC_DATA_IN_CH0_FWD_PWR2 0x1800

- #define ADC_DATA_IN_CH1_FWD_PWR 0x1880

- #define ADC_DATA_IN_CH2_REV_PWR 0x1900

- #define ADC_DATA_IN_CH3_ALC_OUT 0x1980

dataOut:

Constant 0x7FFF

Sending 4 each for each channel every 100ms, so the pipeline is flushed completely for each channel before moving on

From the datasheet it looks like config is entirely contained in every request, but did I miss something?

Is there a one time init sequence?

Or something on the hardware side during reset?

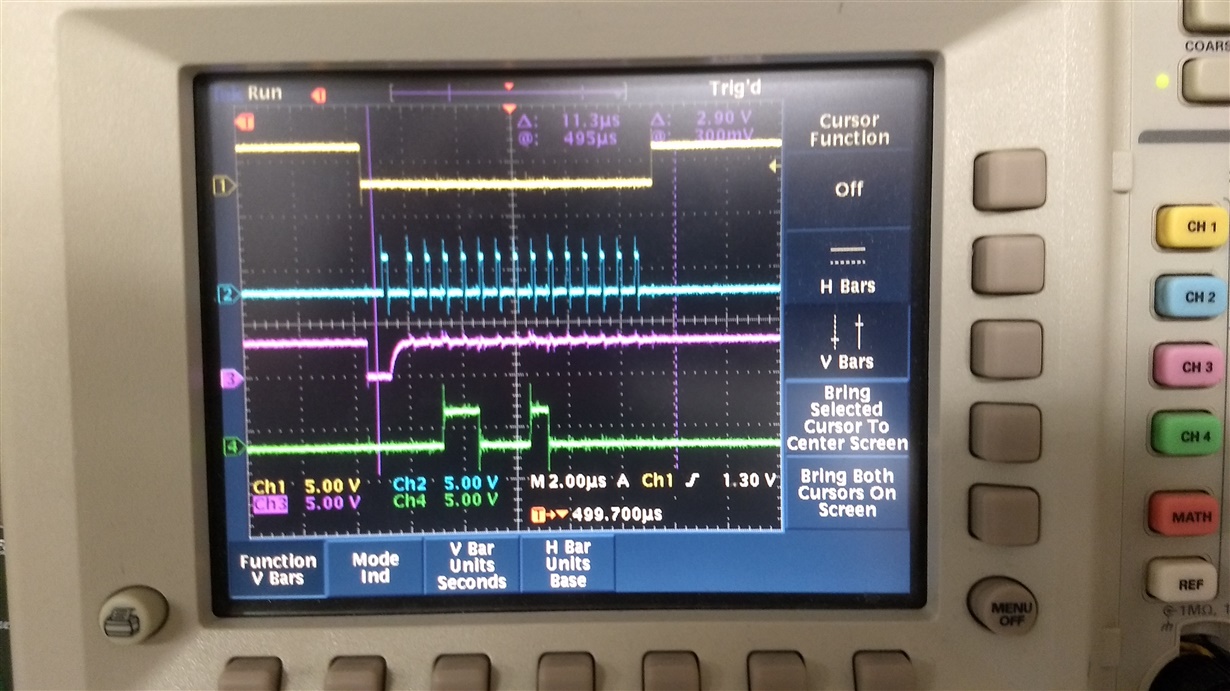

fromtop_cs_sclk_sdo_sdi_2us..jpg

rf_power_measurement_schematic.png